## LKS32MC08x User Manual

© 2019 All rights reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited.

©2019 All rights reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited.

## **CONTENT**

| CO | CONTENTII |           |                                  |  |  |  |

|----|-----------|-----------|----------------------------------|--|--|--|

| LI | ST O      | OF TABLES | SI                               |  |  |  |

| LI | ST O      | )F FIGURE | ES1                              |  |  |  |

| 1  | D         | OCUMEN'   | T CONVENTION1                    |  |  |  |

|    | 1.1       | Registe   | R READ/WRITE PERMISSIONS         |  |  |  |

|    | 1.2       | Abbrev    | IATIONS1                         |  |  |  |

| 2  | A         | DDRESS S  | SPACE3                           |  |  |  |

| 3  | IN        | NTERRUP   | T4                               |  |  |  |

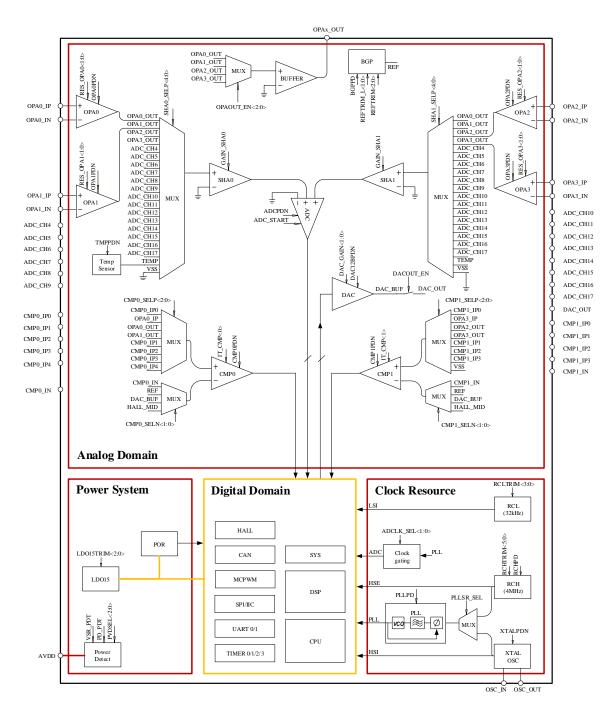

| 4  | A         | NALOG CI  | IRCUIT5                          |  |  |  |

|    | 4.1       | INTROD    | UCTION5                          |  |  |  |

|    | 4.2       | Power     | MANAGEMENT SYSTEM (POWER)        |  |  |  |

|    | 4.3       | CLOCK S   | узтем (CLOCK)7                   |  |  |  |

|    | 4.4       | BANDGA    | AP VOLTAGE REFERENCE (BGP)       |  |  |  |

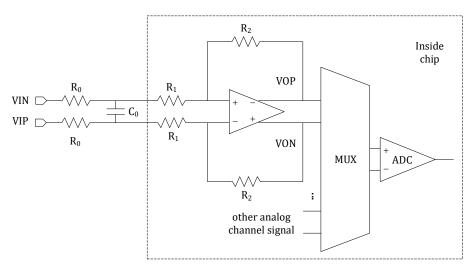

|    | 4.5       | Analog    | S-TO-DIGITAL CONVERTER (ADC)     |  |  |  |

|    | 4.6       | Operat    | IONAL AMPLIFIER (OPA)            |  |  |  |

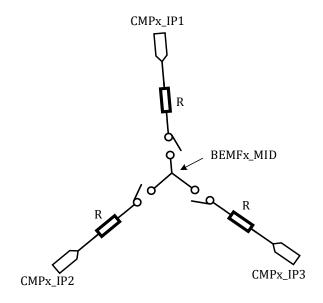

|    | 4.7       | Сомран    | RATOR (CMP)9                     |  |  |  |

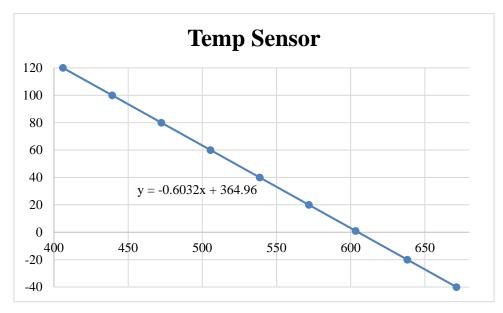

|    | 4.8       | Temper    | ATURE SENSOR (TMP)               |  |  |  |

|    | 4.9       | DIGITAL   | -to-analog Converter (DAC)       |  |  |  |

| 5  | S         | YSTEM CO  | ONTROL AND CLOCK RESET14         |  |  |  |

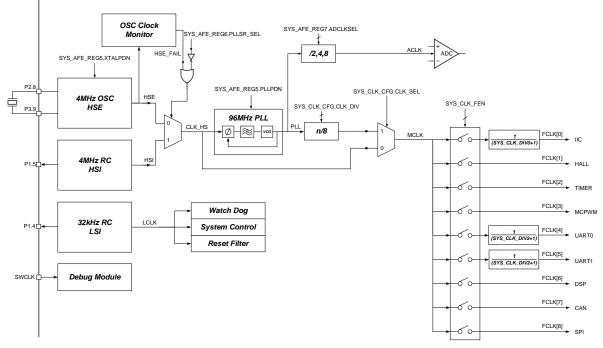

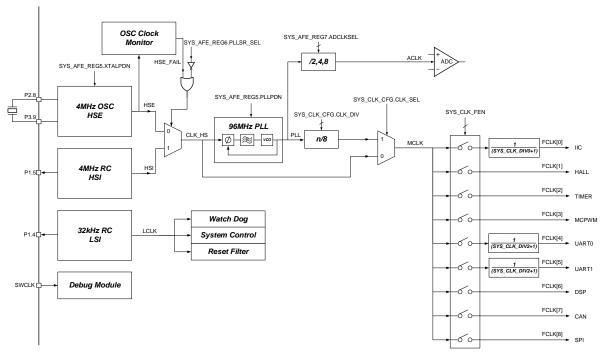

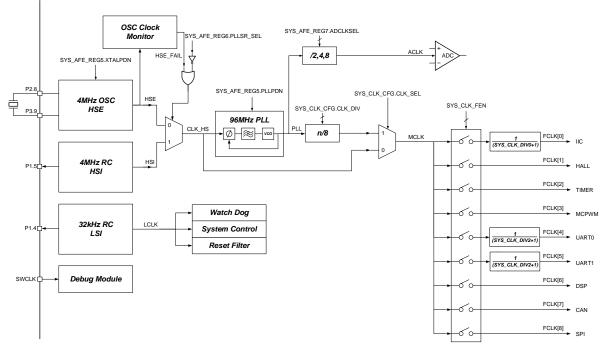

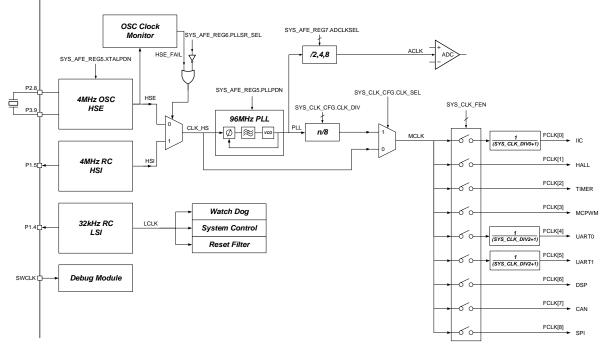

|    | 5.1       | System    | Сьоск                            |  |  |  |

|    | 5.        | .1.1 Cloc | k Source                         |  |  |  |

|    | 5.        | 1.2 Pow   | er Management and Sleep Wakeup16 |  |  |  |

|    |           | 5.1.2.1   | Sleep16                          |  |  |  |

|    |           | 5.1.2.2   | Wakeup                           |  |  |  |

|    |           | 5.1.2.3   | Peripheral Clock Gating (PCG)17  |  |  |  |

|    |           | 5.1.2.4   | Peripheral Clock Divider18       |  |  |  |

|    | 5.2       | RESET     |                                  |  |  |  |

$\verb"©2019 All rights reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. \\$

|    | 5.2.1  | Reset Source                                                                         | 19 |

|----|--------|--------------------------------------------------------------------------------------|----|

|    | 5.2.1  | .1 Hardware Reset                                                                    | 19 |

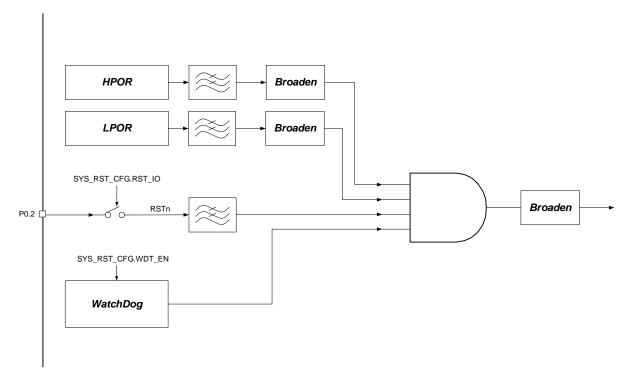

|    | 5.     | 2.1.1.1 Hardware Reset Architecture                                                  | 19 |

|    | 5.     | 2.1.1.2 Hardware Reset Records                                                       | 20 |

|    | 5.2.1  | .2 Software Reset                                                                    | 20 |

| 5. | 3 Ri   | EGISTER                                                                              | 21 |

|    | 5.3.1  | Address Allocation                                                                   | 21 |

|    | 5.3.2  | SYS_AFE_CMP Comparator output register                                               | 22 |

|    | 5.3.3  | Introduction to Analog Register                                                      | 22 |

|    | 5.3.4  | AFE Register 0 (SYS_AFE_REG0)                                                        | 22 |

|    | 5.3.5  | AFE Register 1 (SYS_AFE_REG1)                                                        | 24 |

|    | 5.3.6  | AFE Register 2 (SYS_AFE_REG2)                                                        | 25 |

|    | 5.3.7  | AFE Register 3 (SYS_AFE_REG3)                                                        | 25 |

|    | 5.3.8  | AFE Register 4 (SYS_AFE_REG4)                                                        | 27 |

|    | 5.3.9  | AFE Register 5 (SYS_AFE_REG5)                                                        | 28 |

|    | 5.3.10 | AFE Register 6 (SYS_AFE_REG6)                                                        | 29 |

|    | 5.3.11 | AFE Register 7 (SYS_AFE_REG7)                                                        | 30 |

|    | 5.3.12 | DAC Digital Register (SYS_AFE_DAC)                                                   | 31 |

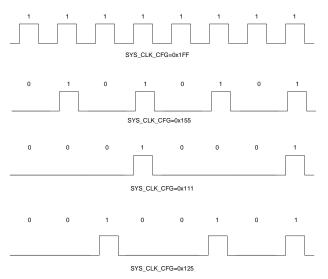

|    | 5.3.13 | Clock Control Register (SYS_CLK_CFG)                                                 | 31 |

|    | 5.3.14 | Reset Control Register (SYS_RST_CFG)                                                 | 32 |

|    | 5.3.15 | Reset Source Record Register (SYS_RST_SRC)                                           | 33 |

|    | 5.3.16 | Reset Source Record Clear Register (SYS_CLR_RST)                                     | 33 |

|    | 5.3.17 | Peripheral Clock Divider Register 0 (SYS_CLK_DIV0)                                   | 34 |

|    | 5.3.18 | Peripheral Clock Divider Register 2 (SYS_CLK_DIV2)                                   | 34 |

|    | 5.3.19 | Peripheral Clock-Gating Register (SYS_CLK_FEN)                                       | 35 |

|    | 5.3.20 | Sleep Register (SYS_CLK_SLP)                                                         | 35 |

|    | 5.3.21 | Correction Mode Register (SYS_TRIM)                                                  | 36 |

|    | 5.3.22 | Soft Reset Register (SYS_SFT_RST)                                                    | 36 |

|    | 5.3.23 | Write Protection Register (SYS_WR_PROTECT)                                           | 37 |

|    | 5.3.24 | DAC Gain Correction Register (SYS_AFE_DAC_AMC)                                       | 37 |

| 9  | s res  | erved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. |    |

|    | 5.3.2 | 25         | DAC DC Offset Register (SYS_AFE_DAC_DC)                                          |        |

|----|-------|------------|----------------------------------------------------------------------------------|--------|

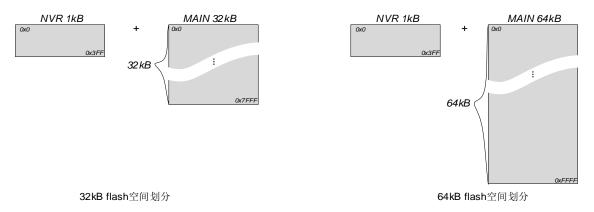

| 6  | FLA   | SH         |                                                                                  |        |

|    | 6.1   | Intro      | DUCTION                                                                          |        |

|    | 6.2   | Featu      | IRES                                                                             | 39     |

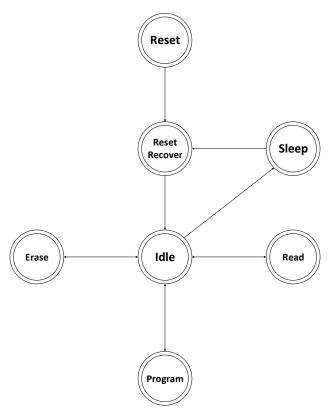

|    | 6.2.2 | 1 Fu       | nctional Description                                                             | 40     |

|    | 6.    | .2.1.1     | Reset                                                                            | 40     |

|    | 6.    | .2.1.2     | Sleep                                                                            | 40     |

|    | 6.    | .2.1.3     | FLASH Read                                                                       | 41     |

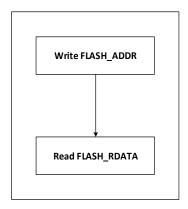

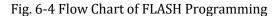

|    | 6.    | .2.1.4     | FLASH Programming                                                                | 41     |

|    | 6.    | .2.1.5     | FLASH Erase                                                                      | 43     |

|    | 6.    | .2.1.6     | FLASH Prefetch                                                                   | 44     |

|    | 6.    | .2.1.7     | FLASH Encryption                                                                 | 44     |

|    | 6.    | .2.1.8     | FLASH Online Upgrade (IAP)                                                       | 45     |

|    |       | 6.2.1.     | 8.1 Start Interrupted Online Upgrade                                             | 45     |

|    |       | 6.2.1.     | 8.2 End Interrupted Online Upgrade                                               | 46     |

|    |       | 6.2.1.     | 8.3 Location of Online Upgrade Function                                          | 46     |

|    | 6.3   | Regis      | TER                                                                              | 46     |

|    | 6.3.1 | 1 Aa       | Idress Allocation                                                                |        |

|    | 6.3.2 | 2 FL       | ASH_CFG Configuration Register (Read back first, and then modify by the OR/AND f | orm)47 |

|    | 6.3.3 | 3 Aa       | ldress Register (FLASH_ADDR)                                                     |        |

|    | 6.3.4 | 4 W        | rite Register (FLASH_WDATA)                                                      |        |

|    | 6.3.5 | 5 Re       | ad Register (FLASH_RDATA)                                                        | 49     |

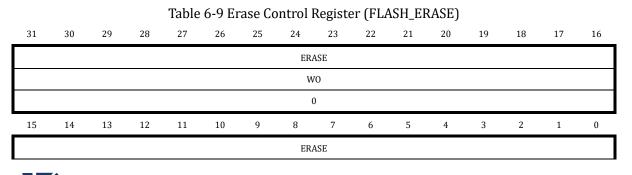

|    | 6.3.6 | 6 Ere      | ase Control Register (FLASH_ERASE)                                               |        |

|    | 6.3.7 | 7 En       | cryption Status Register (FLASH_PROTECT)                                         |        |

|    | 6.3.8 | 8 W        | orking Status Register (FLASH_READY)                                             |        |

|    | 6.3.9 | 9 NI       | VR correction value address information                                          | 51     |

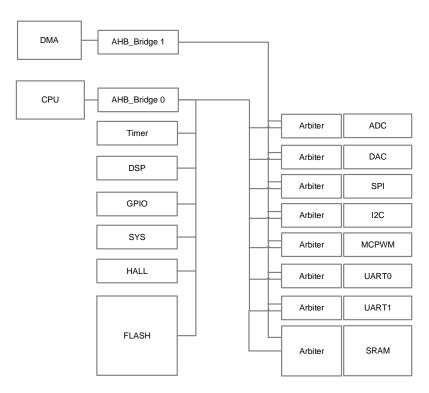

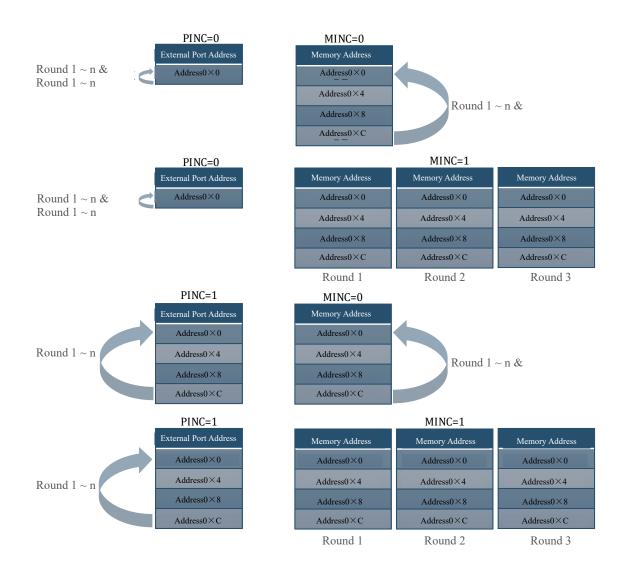

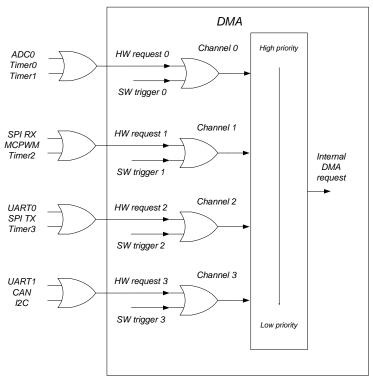

| 7  | DM    | A          | -<br>                                                                            | 54     |

|    | 7.1   | Intro      | DUCTION                                                                          | 54     |

|    | 7.2   | Requ       | EST                                                                              | 56     |

|    | 7.3   | Prior      | ITY                                                                              | 57     |

| ©2 |       | s reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited.   | iii    |

|    | 7.4   | Arbitration                                                                               | 58 |

|----|-------|-------------------------------------------------------------------------------------------|----|

|    | 7.5   | INTERRUPT                                                                                 | 58 |

|    | 7.6   | REGISTER                                                                                  | 59 |

|    | 7.6.1 | 1 Address Allocation                                                                      | 59 |

|    | 7.6.2 | 2 DMA Controller Register (DMA_CTRL)                                                      | 59 |

|    | 7.6.3 | 3 DMA Interrupt Flag Register (DMA_IF)                                                    | 60 |

|    | 7.6.4 | 4 DMA Channel Configuration Register                                                      | 60 |

|    | 7.    | .6.4.1 DMA_CCRx (where x = 0,1,2,3)                                                       | 60 |

|    | 7.    | .6.4.2 DMA_CTMSx (where x = 0,1,2,3)                                                      | 62 |

|    | 7.    | .6.4.3 DMA_CPARx (where x = 0,1,2,3)                                                      | 62 |

|    | 7.    | .6.4.4 DMA_CMARx (where x = 0,1,2,3)                                                      | 63 |

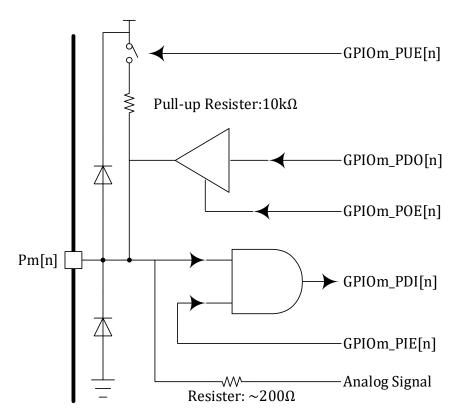

| 8  | GPI   | 0                                                                                         | 65 |

|    | 8.1   | INTRODUCTION                                                                              | 65 |

|    | 8.1.1 | 1 Functional Block Diagram                                                                | 65 |

|    | 8.1.2 | 2 Features                                                                                | 66 |

|    | 8.2   | Register                                                                                  | 66 |

|    | 8.2.1 | 1 Address Allocation                                                                      | 66 |

|    | 8.2.2 | 2 GPIOx_PIE                                                                               | 67 |

|    | 8.2.3 | 3 GPIOx_POE                                                                               | 68 |

|    | 8.2.4 | 4 GPIOx_PDI                                                                               | 69 |

|    | 8.2.5 | 5 GPIOx_PDO                                                                               | 69 |

|    | 8.2.6 | 6 GPIOx_PUE                                                                               | 69 |

|    | 8.2.7 | 7 GPIOx_PODE                                                                              | 70 |

|    | 8.2.8 | 8 GPIOx_LCKR                                                                              | 71 |

|    | 8.2.9 | 9 GPIOx_F3210                                                                             | 72 |

|    | 8.2.1 | 10 GPIOx_F7654                                                                            | 73 |

|    | 8.2.1 | 11 GPIOx_FBA98                                                                            | 73 |

|    | 8.2.1 | 12 GPIOx_FFEDC                                                                            | 74 |

|    | 8.2.1 | 13 External Interrupt, Wake-up, Lock Protection                                           | 74 |

| _  | 8.    | .2.13.1 EXTI_CR0                                                                          | 74 |

| ©2 |       | s reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. |    |

|      | 8.2.1  | 13.2 EXTI_CR1                                                                         | .76 |

|------|--------|---------------------------------------------------------------------------------------|-----|

|      | 8.2.1  | 13.3 EXTI_IF                                                                          | .77 |

|      | 8.2.1  | L3.4 LCKR_PRT                                                                         | .78 |

|      | 8.2.1  | 13.5 WAKE_POL                                                                         | .79 |

|      | 8.2.1  | 13.6 WAKE_EN                                                                          | .79 |

| 8    | .3 F   | unction Implementation                                                                | 80  |

|      | 8.3.1  | Pull-up                                                                               | 80  |

| 8    | .4 A   | PPLICATION GUIDE                                                                      | 80  |

|      | 8.4.1  | Configuration Lock                                                                    | 80  |

|      | 8.4.2  | External Interrupt                                                                    | 82  |

|      | 8.4.3  | GPIO Analog Mode                                                                      | 83  |

| 9    | CRC    |                                                                                       | 84  |

| 9    | .1 IN  | ITRODUCTION                                                                           | 84  |

| 9    | .2 B   | ASIC PRINCIPLES                                                                       | 84  |

| 9    | .3 B   | ASIC CONCEPTS                                                                         | 84  |

|      | 9.3.1  | Correspondence                                                                        | 84  |

|      | 9.3.2  | Generator Polynomial                                                                  | 85  |

|      | 9.3.3  | CRC Digits                                                                            | 85  |

|      | 9.3.4  | Generation Steps                                                                      | 85  |

| 9    | .4 R   | EGISTER                                                                               | 87  |

|      | 9.4.1  | Address Allocation                                                                    | 87  |

|      | 9.4.2  | Register Description                                                                  | 87  |

|      | 9.4.2  | 2.1 CRC Data Register (CRC_DR)                                                        | .87 |

|      | 9.4.2  | 2.2 CRC Control Register (CRC_CR)                                                     | .88 |

|      | 9.4.2  | 2.3 CRC Initial Code Register (CRC_INIT)                                              | .89 |

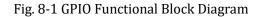

|      | 9.4.2  | 2.4 CRC Generation Code Register (CRC_POL)                                            | .89 |

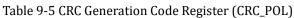

| 10   | ADO    | 2                                                                                     | 90  |

| 1    | 0.1 IN | ITRODUCTION                                                                           | 90  |

|      | 10.1.1 | Functional Block Diagram                                                              | 91  |

| _    | 10.1.2 | ADC Trigger Mode                                                                      | 92  |

| ©2 9 | s res  | served by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. |     |

| 10.1 | 1.3         | ADC Analog Channel                                                             |    | 94  |

|------|-------------|--------------------------------------------------------------------------------|----|-----|

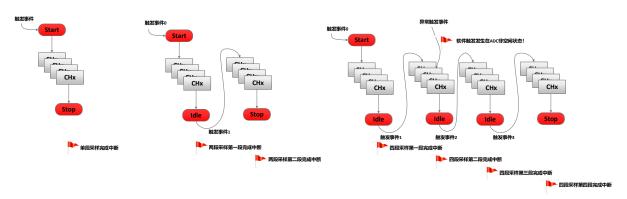

| 10.1 | 1.4         | ADC Interrupt                                                                  |    | 94  |

| 10.1 | 1.5         | ADC Output Digital System                                                      |    | 95  |

| 10.1 | 1.6         | ADC Reference Voltage and Range                                                |    | 95  |

| 1    | 0.1.6.1     | 2.4V Reference Voltage Mode                                                    |    | 95  |

| 1    | 0.1.6.2     | 1.2V Reference Voltage Mode                                                    |    | 96  |

| 10.  | 1.7         | ADC Calibration                                                                |    | 96  |

| 10.  | 1.8         | ADC configuration process                                                      |    | 97  |

| 10.2 | REGIS       | TER                                                                            |    | 98  |

| 10.2 | 2.1         | Address Allocation                                                             |    | 98  |

| 10.2 | 2.2         | Sampling Data Register                                                         |    | 99  |

| 1    | 0.2.2.1     | ADC0_DAT0                                                                      |    | 99  |

| 1    | 0.2.2.2     | ADC0_DAT1                                                                      |    | 100 |

| 1    | 0.2.2.3     | ADC0_DAT2                                                                      |    | 100 |

| 1    | 0.2.2.4     | ADC0_DAT3                                                                      |    | 101 |

| 1    | 0.2.2.5     | ADC0_DAT4                                                                      |    | 101 |

| 1    | 0.2.2.6     | ADC0_DAT5                                                                      |    | 101 |

| 1    | 0.2.2.7     | ADC0_DAT6                                                                      |    | 102 |

| 1    | 0.2.2.8     | ADC0_DAT7                                                                      |    | 102 |

| 1    | 0.2.2.9     | ADC0_DAT8                                                                      |    | 103 |

| 1    | 0.2.2.1     | 0 ADC0_DAT9                                                                    |    | 103 |

| 1    | 0.2.2.1     | 1 ADC0_DAT10                                                                   |    | 103 |

| 1    | 0.2.2.1     | 2 ADC0_DAT11                                                                   |    | 104 |

| 1    | 0.2.2.1     | 3 ADC0_DAT12                                                                   |    | 104 |

| 1    | 0.2.2.1     | 4 ADC_DAT13                                                                    |    | 105 |

| 1    | 0.2.2.1     | 5 ADC0_DAT14                                                                   |    | 105 |

| 1    | 0.2.2.1     | 6 ADC0_DAT15                                                                   |    | 105 |

| 1    | 0.2.2.1     | 7 ADC0_DAT16                                                                   |    | 106 |

| 1    | 0.2.2.1     | 8 ADC0_DAT17                                                                   |    | 106 |

| 1    | 0.2.2.1     | 9 ADC0_DAT18                                                                   |    | 107 |

|      | es reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | vi |     |

| 10.2.2.20     | ADC0_DAT19                                                                    |     |

|---------------|-------------------------------------------------------------------------------|-----|

| 10.2.3 S      | ignal Source Register                                                         |     |

| 10.2.3.1      | ADC0_CHN0                                                                     | 107 |

| 10.2.3.2      | ADC0_CHN1                                                                     |     |

| 10.2.3.3      | ADC0_CHN2                                                                     |     |

| 10.2.3.4      | ADC0_CHN3                                                                     |     |

| 10.2.3.5      | ADC0_CHN4                                                                     |     |

| 10.2.3.6      | ADC0_CHN5                                                                     | 110 |

| 10.2.3.7      | ADC0_CHN6                                                                     | 110 |

| 10.2.3.8      | ADC0_CHN7                                                                     | 111 |

| 10.2.3.9      | ADC0_CHN8                                                                     | 111 |

| 10.2.3.10     | ADC0_CHN9                                                                     | 112 |

| 10.2.4 S      | ampling times Register                                                        |     |

| 10.2.4.1      | ADC0_CHNT0                                                                    |     |

| 10.2.4.2      | - ADC0_CHNT1                                                                  |     |

| 10.2.5 C      | -<br>Configuration Register                                                   |     |

| 10.2.5.1      | ADC0_CFG                                                                      |     |

| 10.2.5.2      | ADC0_TRIG                                                                     |     |

|               | Gain Selection Register                                                       |     |

| 10.2.0        | ADC0_GAIN0                                                                    |     |

|               |                                                                               |     |

| 10.2.6.2      | ADC0_GAIN1                                                                    |     |

|               | nterrupt Enable Register                                                      |     |

| 10.2.7.1      | ADC0_IE                                                                       |     |

| 10.2.7.2      | ADC0_IF                                                                       |     |

| 10.2.8 S      | oftware Trigger Register                                                      | 119 |

| 10.2.8.1      | ADC0_SWT                                                                      | 119 |

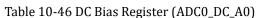

| 10.2.9 D      | DC Bias Register                                                              | 119 |

| 10.2.9.1      | ADC0_DC_A0                                                                    | 119 |

| 10.2.9.2      | ADC0_DC_A1                                                                    |     |

| 10.2.9.3      | ADC0_DC_B0                                                                    | 120 |

| 9 teserved by | y Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | vii |

| 10.2.9.4        | ADC0_DC_B1                                                                     | 120  |

|-----------------|--------------------------------------------------------------------------------|------|

| 10.2.10         | Gain Calibration Register                                                      |      |

| 10.2.10.        | 1 ADC0_AMC_A0                                                                  | 121  |

| 10.2.10.        | 2 ADC0_AMC_A1                                                                  | 121  |

| 10.2.10.        | 3 ADC0_AMC_B0                                                                  | 122  |

| 10.2.10.        | 4 ADC0_AMC_B1                                                                  | 122  |

| 10.2.11         | Threshold Register for Channel 0                                               |      |

| 10.2.11.        | 1 ADC0_DAT0_TH                                                                 | 123  |

| 10.3 Imple      | MENTATION DESCRIPTION                                                          |      |

| 10.3.1          | DMA Request                                                                    |      |

| 10.3.2          | Continuous Sampling                                                            | 124  |

| 10.4 Appli      | CATION GUIDE                                                                   |      |

| 10.4.1          | ADC Sampling Trigger Mode                                                      |      |

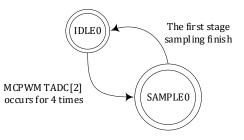

| 10.4.1.1        | Single-round Trigger Mode                                                      | 126  |

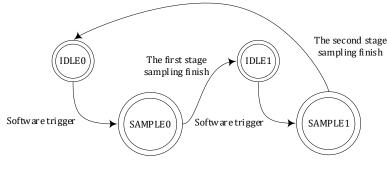

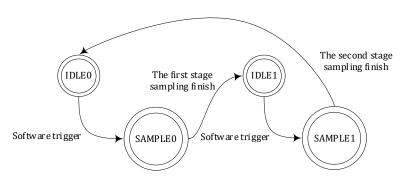

| 10.4.1.2        | Two-round Trigger Mode                                                         | 127  |

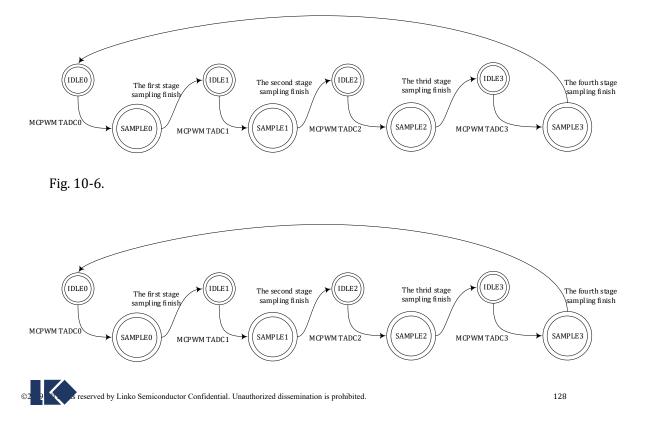

| 10.4.1.3        | Four-round Trigger Mode                                                        | 128  |

| 10.4.2          | Interrupt                                                                      |      |

| 10.4.2.1        | Done Interruption of Single Round Trigger Sampling                             | 129  |

| 10.4.2.2        | Done Interruption of Two Round Trigger Sampling                                | 129  |

| 10.4.2.3        | Done Interruption of Four Round Trigger Sampling                               | 129  |

| 10.4.3          | Configuration Modification                                                     |      |

| 10.4.4          | Select the Corresponding Analog Channel                                        |      |

| 11 GENER        | AL TIMER                                                                       | 131  |

| 11.1 INTRO      | DUCTION                                                                        |      |

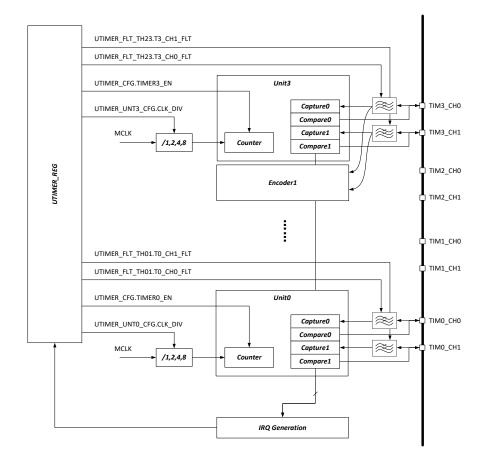

| 11.1.1          | Functional Block Diagram                                                       | 131  |

| 11.1.1.1        | Bus Interface Module                                                           | 131  |

| 11.1.1.2        | Register Module                                                                | 132  |

| 11.1.1.3        | IO Filter Module                                                               | 132  |

| 11.1.1.4        | General Timer Module                                                           | 132  |

| 11.1.1.5        | Encoder Module                                                                 | 132  |

| ©2 9 s reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | viii |

|    | 11.1.1.6       | Clock Divider Module                                                           |    | 132 |

|----|----------------|--------------------------------------------------------------------------------|----|-----|

|    | 11.1.2         | Features                                                                       |    | 132 |

| -  | 11.2 Imple     | MENTATION DESCRIPTION                                                          |    | 133 |

|    | 11.2.1         | Clock Divider                                                                  |    | 133 |

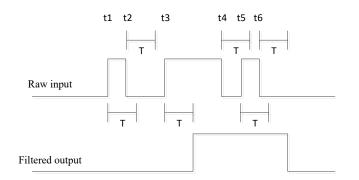

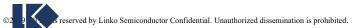

|    | 11.2.2         | Filtering                                                                      |    | 133 |

|    | 11.2.3         | Mode                                                                           |    | 133 |

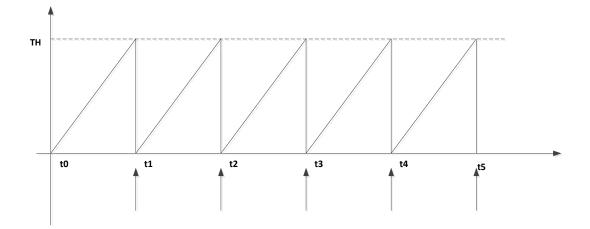

|    | 11.2.3.1       | Counter                                                                        |    | 133 |

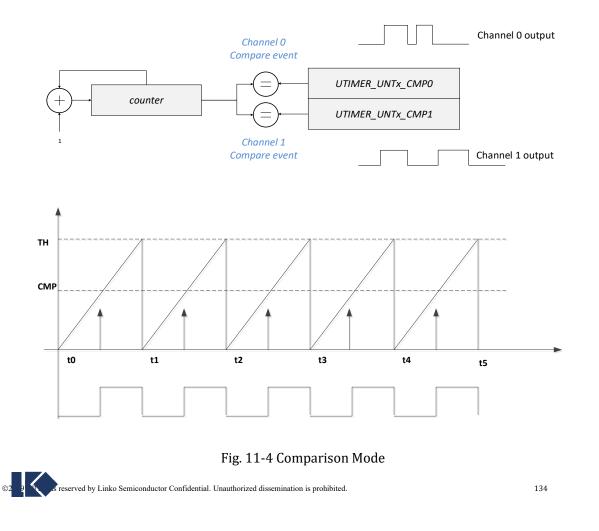

|    | 11.2.3.2       | Comparison Mode                                                                |    | 134 |

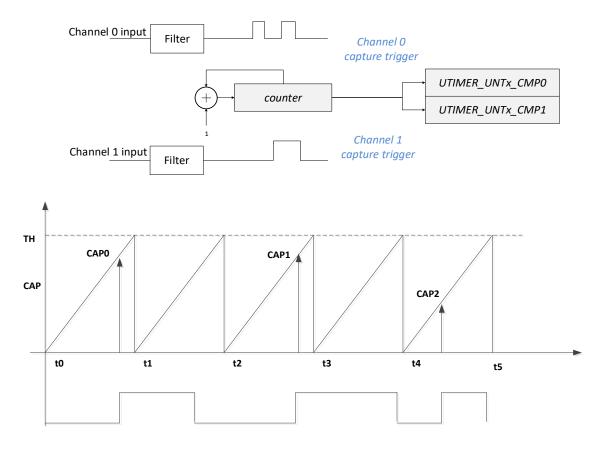

|    | 11.2.3.3       | Capture Mode                                                                   |    | 135 |

|    | 11.2.4         | Encoder                                                                        |    | 135 |

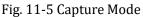

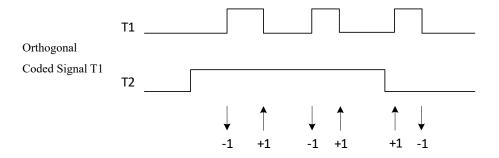

|    | 11.2.4.1       | Orthogonal Coded Signal                                                        |    | 135 |

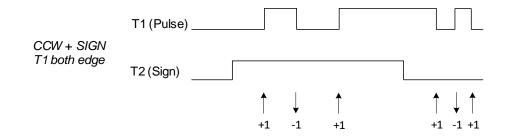

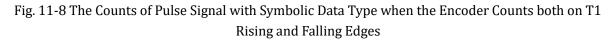

|    | 11.2.4.2       | Pulse Signal with Symbolic Data Type                                           |    | 137 |

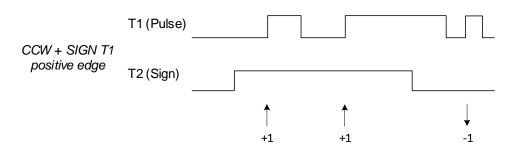

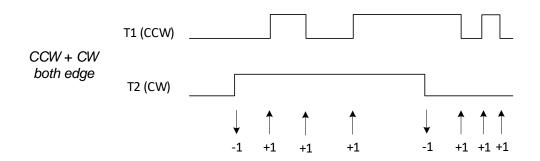

|    | 11.2.4.3       | CCW/CW Double Pulse Signal                                                     |    | 138 |

| -  | 11.3 Regis     | TER                                                                            |    | 139 |

|    | 11.3.1         | Address Allocation                                                             |    | 139 |

|    | 11.3.2         | System Control Register                                                        |    | 140 |

|    | 11.3.2.1       | UTIMER_CFG                                                                     |    | 140 |

|    | 11.3.3         | Filter Control Register                                                        |    | 141 |

|    | 11.3.3.1       | UTIMER_FLT_TH01                                                                |    | 141 |

|    | 11.3.3.2       | UTIMER_FLT_TH23                                                                |    | 141 |

|    | 11.3.4         | Timer Register                                                                 |    | 142 |

|    | 11.3.4.1       | Timer0 Configuration Register (UTIMER_UNT0_CFG)                                |    | 142 |

|    | 11.3.4.2       | Timer1 Configuration Register (UTIMER_UNT1_CFG)                                |    | 144 |

|    | 11.3.4.3       | Timer2 Configuration Register (UTIMER_UNT2_CFG)                                |    | 145 |

|    | 11.3.4.4       | Timer3 Configuration Register (UTIMER_UNT3_CFG)                                |    | 146 |

|    | 11.3.4.5       | Timer 0 Threshold Register (UTIMER_UNT0_TH)                                    |    | 148 |

|    | 11.3.4.6       | Timer 1 Threshold Register (UTIMER_UNT1_TH)                                    |    | 148 |

|    | 11.3.4.7       | Timer 2 Threshold Register (UTIMER_UNT2_TH)                                    |    | 149 |

|    | 11.3.4.8       | Timer 3 Threshold Register (UTIMER_UNT3_TH)                                    |    | 149 |

|    | 11.3.4.9       | Timer 0 Count Register (UTIMER_UNT0_CNT)                                       |    | 150 |

| ©2 | 9 . s reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | ix |     |

|      | 11.3.4.1  | 0 Timer 1Count Register (UTIMER_UNT1_CNT)                                        | 150 |

|------|-----------|----------------------------------------------------------------------------------|-----|

|      | 11.3.4.1  | 1 Timer 2 Counter Register (UTIMER_UNT2_CNT)                                     | 150 |

|      | 11.3.4.1  | 2 Timer 3 Count Register (UTIMER_UNT3_CNT)                                       | 151 |

|      | 11.3.4.1  | 3 Timer 0 Channel 0 Compare Capture Register (UTIMER_UNT0_CMP0)                  | 151 |

|      | 11.3.4.1  | 4 Timer 0 Channel 1 Compare Capture Register (UTIMER_UNT0_CMP1)                  | 152 |

|      | 11.3.4.1  | 5 Timer 1 Channel 0 Compare Capture Register (UTIMER_UNT1_CMP0)                  | 152 |

|      | 11.3.4.1  | 6 Timer 1 Channel 0 Compare Capture Register (UTIMER_UNT1_CMP1)                  | 153 |

|      | 11.3.4.1  | Timer 2 Channel 0 Compare Capture Register (UTIMER_UNT2_CMP0)                    | 153 |

|      | 11.3.4.1  | 8 Timer 2 Channel 1 Compare Capture Register (UTIMER_UNT2_CMP1)                  | 154 |

|      | 11.3.4.1  | 9 Timer 3 Channel 0 Compare Capture Register (UTIMER_UNT3_CMP0)                  | 154 |

|      | 11.3.4.2  | 20 Timer 3 Channel 1 Compare Capture Register (UTIMER_UNT3_CMP1)                 | 155 |

|      | 11.3.4.2  | Timer0 External Event Select Register (UTIMER_UNT0_EVT)                          | 156 |

|      | 11.3.4.2  | 22 Timer1 External Event Select Register (UTIMER_UNT1_EVT)                       | 156 |

|      | 11.3.4.2  | Timer2 External Event Select Register (UTIMER_UNT2_EVT)                          | 157 |

|      | 11.3.4.2  | Timer3 External Event Select Register (UTIMER_UNT3_EVT)                          | 157 |

|      | 11.3.5    | Encoder Register                                                                 |     |

|      | 11.3.5.1  | EncoderX Configuration Register (UTIMER_ECDx_CFG)                                | 158 |

|      | 11.3.5.2  | 2 EncoderX Count Threshold Register (UTIMER_ECDx_TH )                            | 159 |

|      | 11.3.5.3  | B EncoderX Count Value Register (UTIMER_ECDx_CNT)                                | 159 |

|      | 11.3.6    | Interrupt Management Register                                                    |     |

|      | 11.3.6.1  | Interrupt Enable Register (UTIMER_IE)                                            | 160 |

|      | 11.3.6.2  | 2 Interrupt Flag Register (UTIMER_IF)                                            | 161 |

|      | 11.3.7    | DMA Management Register                                                          |     |

|      | 11.3.7.1  | DMA Request Enable Register (UTIMER_RE)                                          | 162 |

| 12   | HALL      | SIGNAL PROCESSING MODULE                                                         | 164 |

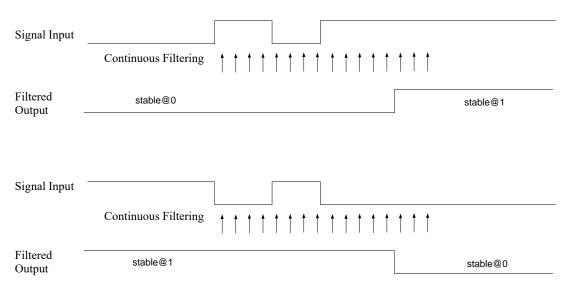

| 1    | 2.1 Intro | DDUCTION                                                                         | 164 |

| 1    | 2.2 Impl  | EMENTATION DESCRIPTION                                                           | 164 |

|      | 12.2.1    | Signal Source                                                                    |     |

|      | 12.2.2    | System Clock                                                                     | 164 |

|      | 12.2.3    | Signal Filtering                                                                 |     |

| ©2 9 | s reserve | d by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | x   |

|    | 12.2.4    | Capture                                                                              | 165 |

|----|-----------|--------------------------------------------------------------------------------------|-----|

|    | 12.2.5    | Interrupt                                                                            | 166 |

|    | 12.2.6    | Data Flow                                                                            | 166 |

| 1  | 2.3 Regi  | STER                                                                                 | 166 |

|    | 12.3.1    | Address Allocation                                                                   | 166 |

|    | 12.3.2    | HALL Module Configuration Register (HALL_CFG)                                        | 166 |

|    | 12.3.3    | HALL Module Information Register (HALL_INFO)                                         | 168 |

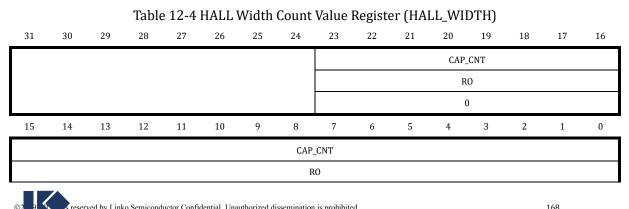

|    | 12.3.4    | HALL Width Count Value Register (HALL_WIDTH)                                         | 168 |

|    | 12.3.5    | HALL Module Counter Threshold Register (HALL_TH)                                     | 169 |

|    | 12.3.6    | HALL Count Register (HALL_CNT)                                                       | 169 |

| 13 | МСРИ      | /M                                                                                   | 171 |

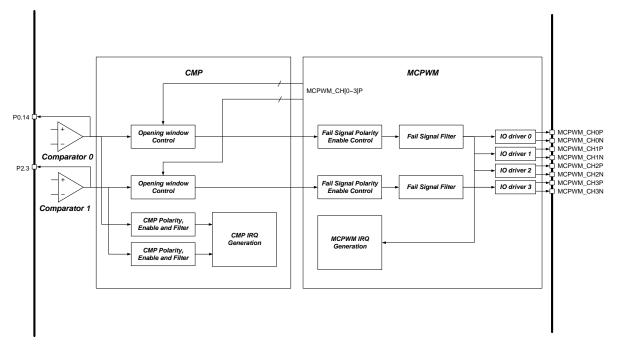

| 1  | 3.1 Intro | ODUCTION                                                                             | 171 |

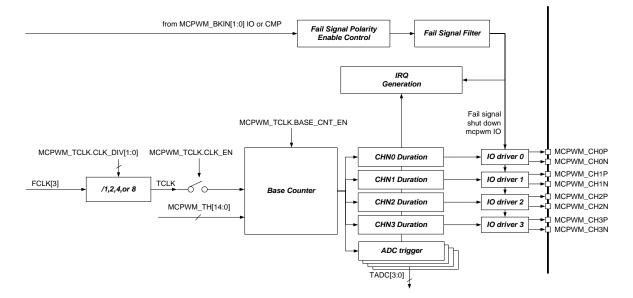

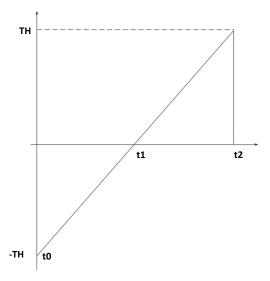

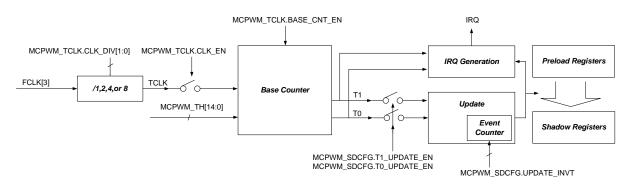

|    | 13.1.1    | Base Counter Module                                                                  | 172 |

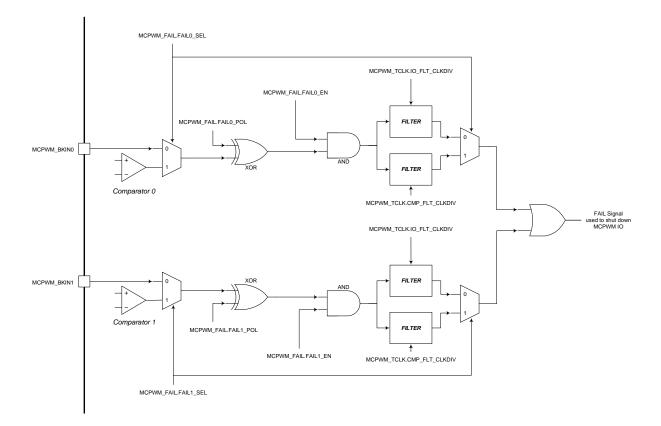

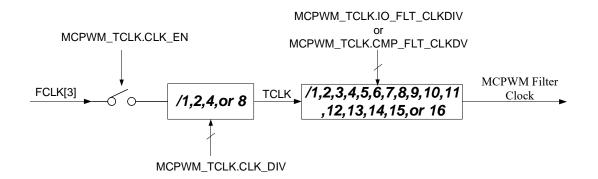

|    | 13.1.2    | Fail Signal Processing                                                               | 173 |

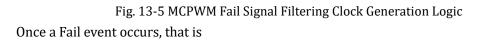

|    | 13.1.3    | MCPWM Special Output Status                                                          | 175 |

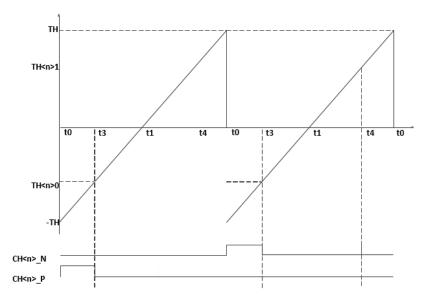

|    | 13.1.4    | IO DRIVER Module                                                                     | 175 |

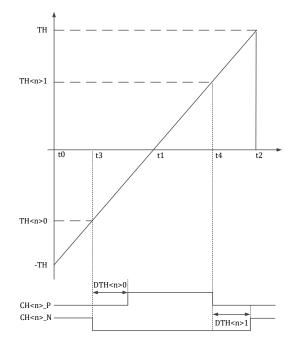

|    | 13.1.4.2  | 1 MCPWM Wave-form Output: Center-aligned Mode                                        | 176 |

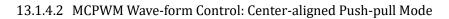

|    | 13.1.4.2  | 2 MCPWM Wave-form Control: Center-aligned Push-pull Mode                             | 177 |

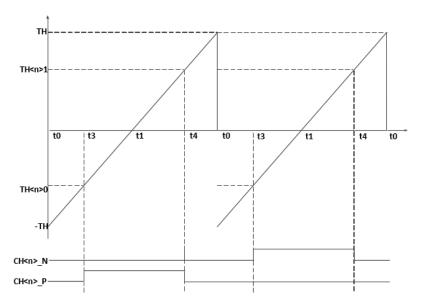

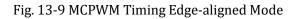

|    | 13.1.4.3  | 3 MCPWM Wave-form Output: Edge-aligned Mode                                          | 177 |

|    | 13.1.4.4  | 4 MCPWM Wave-form Control: Edge-aligned Push-pull Mode                               | 178 |

|    | 13.1.4.5  | 5 MCPWM IO: Dead-zone Control                                                        | 179 |

|    | 13.1.4.6  | 6 MCPWM IO: Polarity Setting                                                         | 179 |

|    | 13.1.4.2  | 7 MCPWM IO: Auto-protection                                                          | 180 |

|    | 13.1.5    | ADC Trigger Timer Module                                                             | 180 |

|    | 13.1.6    | MCPWM Main Events                                                                    | 180 |

| 1  | 3.2 Regi  | STER                                                                                 | 181 |

|    | 13.2.1    | Address Allocation                                                                   | 181 |

|    | 13.2.2    | MCPWM_TH00                                                                           | 183 |

|    | 13.2.3    | MCPWM_TH01                                                                           | 183 |

| _  | 13.2.4    | MCPWM_TH10                                                                           | 184 |

| ©2 | s reserve | ed by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. xi |     |

|    | 13.2.5     | MCPWM_TH11                                                                        |     |

|----|------------|-----------------------------------------------------------------------------------|-----|

|    | 13.2.6     | MCPWM_TH20                                                                        |     |

|    | 13.2.7     | MCPWM_TH21                                                                        |     |

|    | 13.2.8     | MCPWM_TH30                                                                        |     |

|    | 13.2.9     | MCPWM_TH31                                                                        |     |

|    | 13.2.10    | MCPWM_TMR0                                                                        |     |

|    | 13.2.11    | MCPWM_TMR1                                                                        |     |

|    | 13.2.12    | MCPWM_TMR2                                                                        |     |

|    | 13.2.13    | MCPWM_TMR3                                                                        |     |

|    | 13.2.14    | MCPWM_TH                                                                          |     |

|    | 13.2.15    | MCPWM_UPDATE                                                                      |     |

|    | 13.2.16    | MCPWM_IE                                                                          |     |

|    | 13.2.17    | MCPWM_IF                                                                          |     |

|    | 13.2.18    | MCPWM_EIE                                                                         |     |

|    | 13.2.19    | MCPWM_EIF                                                                         |     |

|    | 13.2.20    | MCPWM_RE                                                                          |     |

|    | 13.2.21    | MCPWM_PP                                                                          |     |

|    | 13.2.22    | MCPWM_I001                                                                        |     |

|    | 13.2.23    | MCPWM_1023                                                                        |     |

|    | 13.2.24    | MCPWM_SDCFG                                                                       |     |

|    | 13.2.25    | MCPWM_TCLK                                                                        |     |

|    | 13.2.26    | MCPWM_FAIL                                                                        |     |

|    | 13.2.27    | MCPWM_PRT                                                                         |     |

|    | 13.2.28    | MCPWM_CNT                                                                         | 202 |

|    | 13.2.29    | MCPWM_DTH00                                                                       |     |

|    | 13.2.30    | MCPWM_DTH01                                                                       |     |

|    | 13.2.31    | MCPWM_DTH10                                                                       |     |

|    | 13.2.32    | MCPWM_DTH11                                                                       | 203 |

|    | 13.2.33    | MCPWM_DTH20                                                                       |     |

|    | 13.2.34    | MCPWM_DTH21                                                                       |     |

| ©2 | es reserve | ed by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xii |

|    | 13.2.35     | MCPWM_DTH30                                                                       | 205  |

|----|-------------|-----------------------------------------------------------------------------------|------|

|    | 13.2.36     | MCPWM_DTH31                                                                       |      |

| 14 | UART        |                                                                                   | 206  |

| 1  | L4.1 INTR   | ODUCTION                                                                          | 206  |

| 1  | L4.2 Pin F  | FUNCTION DESCRIPTION                                                              | 206  |

|    | 14.2.1      | Transport (TX)                                                                    |      |

|    | 14.2.2      | Receive (RX)                                                                      |      |

|    | 14.2.3      | Baud Rate Configuration                                                           |      |

|    | 14.2.4      | DMA Configuration                                                                 |      |

| 1  | L4.3 Regi   | STER                                                                              | 208  |

|    | 14.3.1      | Address Allocation                                                                |      |

|    | 14.3.2      | UARTx Control Register (UARTx_CTRL)                                               |      |

|    | 14.3.3      | UARTx Baud Rate High-byte Register (UARTx_DIVH)                                   | 209  |

|    | 14.3.4      | UARTx Baud Rate Low-byte Register (UARTx_DIVL)                                    | 209  |

|    | 14.3.5      | UARTx Transceiver Buffer Register (UARTx_BUFF)                                    | 210  |

|    | 14.3.6      | UARTx Address Match Register (UARTx_ADR)                                          | 210  |

|    | 14.3.7      | UARTx Status Register (UARTx_STT)                                                 | 210  |

|    | 14.3.8      | UARTx Interrupt Enable Register (UARTx_IE)                                        | 211  |

|    | 14.3.9      | UARTx Interrupt Flag Register (UARTx_IF)                                          | 212  |

|    | 14.3.10     | UARTx IO Toggle Output Register (UARTx_INV)                                       | 213  |

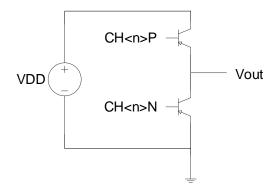

| 15 | DSP         |                                                                                   | 214  |

| 1  | L5.1 INTR   | ODUCTION                                                                          | 214  |

|    | 15.1.1      | Functional Block Diagram                                                          | 215  |

|    | 15.1.2      | DSP Core Register                                                                 | 215  |

|    | 15.1.3      | Bit Width                                                                         | 216  |

|    | 15.1.4      | Instruction Cycle                                                                 | 216  |

|    | 15.1.5      | Address Space                                                                     | 216  |

| 1  | L5.2 Regi   | STER                                                                              | 217  |

|    | 15.2.1      | Address Allocation                                                                | 217  |

|    | 15.2.2      | DSP Status Control Register                                                       | 218  |

| ©2 | 9 s reserve | ed by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xiii |

| 15.2.2.1        | DSP_SC                                                                         | 218 |

|-----------------|--------------------------------------------------------------------------------|-----|

| 15.2.3          | DSP sin/cos Register                                                           | 219 |

| 15.2.3.1        | DSP_THETA                                                                      | 219 |

| 15.2.3.2        | DSP_SIN                                                                        | 219 |

| 15.2.3.3        | DSP_COS                                                                        | 220 |

| 15.2.4          | DSP arctan Register                                                            | 220 |

| 15.2.4.1        | DSP_X                                                                          | 220 |

| 15.2.4.2        | DSP_Y                                                                          | 221 |

| 15.2.4.3        | DSP_MOD                                                                        | 221 |

| 15.2.4.4        | DSP_ARCTAN                                                                     | 222 |

| 15.2.5          | DSP Divider Register                                                           |     |

| 15.2.5.1        | DSP_DID                                                                        | 222 |

| 15.2.5.2        | DSP_DIS                                                                        | 223 |

| 15.2.5.3        | DSP_QUO                                                                        | 223 |

| 15.2.5.4        | DSP_REM                                                                        | 224 |

| 15.2.6          | DSP SQRT Register                                                              |     |

| 15.2.6.1        | DSP_RAD                                                                        | 224 |

| 15.2.6.2        | DSP_SQRT                                                                       | 225 |

| 15.3 DSP I      | NSTRUCTION SET                                                                 | 225 |

| 15.3.1          | Instruction Set Summary                                                        | 225 |

| 15.3.2          | ADD                                                                            | 226 |

| 15.3.2.1        | Encoding                                                                       | 226 |

| 15.3.2.2        | Assembly Syntax                                                                | 226 |

| 15.3.2.3        | Pseudocode                                                                     | 226 |

| 15.3.3          | ADDI (reserved)                                                                | 227 |

| 15.3.3.1        | Instruction Encoding                                                           | 227 |

| 15.3.3.2        | Assembly Syntax                                                                | 227 |

| 15.3.3.3        | Pseudocode                                                                     | 227 |

| 15.3.4          | SUB                                                                            | 227 |

| 15.3.4.1        | Instruction Encoding                                                           | 227 |

| ©2 ? s reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xiv |

|      | 15.3.4.2   | Assembly Syntax                                                                | 227 |

|------|------------|--------------------------------------------------------------------------------|-----|

|      | 15.3.4.3   | Pseudocode                                                                     | 227 |

|      | 15.3.5     | ASR                                                                            |     |

|      | 15.3.5.1   | Instruction Encoding                                                           | 228 |

|      | 15.3.5.2   | Assembly Syntax                                                                | 228 |

|      | 15.3.5.3   | Pseudocode                                                                     | 228 |

|      | 15.3.6     | ASRI                                                                           | 228 |

|      | 15.3.6.1   | Instruction Encoding                                                           | 228 |

|      | 15.3.6.2   | Assembly Syntax                                                                | 228 |

|      | 15.3.6.3   | Pseudocode                                                                     | 228 |

|      | 15.3.7     | LSL                                                                            | 229 |

|      | 15.3.7.1   | Instruction Encoding                                                           | 229 |

|      | 15.3.7.2   | Assembly Syntax                                                                | 229 |

|      | 15.3.7.3   | Pseudocode                                                                     | 229 |

|      | 15.3.8     | LSLI                                                                           | 229 |

|      | 15.3.8.1   | Instruction Encoding                                                           | 229 |

|      | 15.3.8.2   | Assembly Syntax                                                                | 229 |

|      | 15.3.8.3   | Pseudocode                                                                     | 229 |

|      | 15.3.9     | MAC                                                                            | 230 |

|      | 15.3.9.1   | Instruction Encoding                                                           | 230 |

|      | 15.3.9.2   | Assembly Syntax                                                                | 230 |

|      | 15.3.9.3   | Pseudocode                                                                     | 230 |

|      | 15.3.10    | MACI (reserved)                                                                | 230 |

|      | 15.3.10.1  | 1 Instruction Encoding                                                         | 230 |

|      | 15.3.10.2  | 2 Assembly Syntax                                                              | 230 |

|      | 15.3.10.3  | 3 Pseudocode                                                                   | 231 |

|      | 15.3.11    | DIV                                                                            | 231 |

|      | 15.3.11.1  | 1 Instruction Encoding                                                         | 231 |

|      | 15.3.11.2  | 2 Assembly Syntax                                                              | 231 |

| _    | 15.3.11.3  | 3 Pseudocode                                                                   | 231 |

| ©2 9 | s reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xv  |

| 15.3.12 S | AT                                                                            |     |

|-----------|-------------------------------------------------------------------------------|-----|

| 15.3.12.1 | Instruction Encoding                                                          | 231 |

| 15.3.12.2 | Assembly Syntax                                                               | 232 |

| 15.3.12.3 | Pseudocode                                                                    | 232 |

| 15.3.13 S | ATI (reserved)                                                                |     |

| 15.3.13.1 | Instruction Encoding                                                          | 232 |

| 15.3.13.2 | Assembly Syntax                                                               | 232 |

| 15.3.13.3 | Pseudocode                                                                    | 232 |

| 15.3.14 S | CIN_COS                                                                       | 232 |

| 15.3.14.1 | Instruction Encoding                                                          | 232 |

| 15.3.14.2 | Assembly Syntax                                                               | 233 |

| 15.3.14.3 | Pseudocode                                                                    | 233 |

| 15.3.15 A | ARCTAN                                                                        | 233 |

| 15.3.15.1 | Instruction Encoding                                                          | 233 |

| 15.3.15.2 | Assembly Syntax                                                               | 233 |

| 15.3.15.3 | Pseudocode                                                                    | 233 |

| 15.3.16 S | QRT                                                                           | 233 |

| 15.3.16.1 | Instruction Encoding                                                          | 233 |

| 15.3.16.2 | Assembly Syntax                                                               | 233 |

| 15.3.16.3 | Pseudocode                                                                    | 234 |

| 15.3.17 L | DRWI                                                                          | 234 |

| 15.3.17.1 | Instruction Encoding                                                          | 234 |

| 15.3.17.2 | Assembly Syntax                                                               | 234 |

| 15.3.17.3 | Pseudocode                                                                    | 234 |

| 15.3.18 L | DRDHI                                                                         | 234 |

| 15.3.18.1 | Instruction Encoding                                                          | 234 |

| 15.3.18.2 | Assembly Syntax                                                               | 234 |

| 15.3.18.3 | Pseudocode                                                                    | 235 |

| 15.3.19 S | TRWI                                                                          | 235 |

| 15.3.19.1 | Instruction Encoding                                                          | 235 |

| ©2        | y Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xvi |

|    | 15.3.19.2           | Assembly Syntax                                                            | 235  |

|----|---------------------|----------------------------------------------------------------------------|------|

|    | 15.3.19.3           | Pseudocode                                                                 | 235  |

|    | 15.3.20 STF         | RDHI (reserved)                                                            | 235  |

|    | 15.3.20.1           | Instruction Encoding                                                       | 236  |

|    | 15.3.20.2           | Assembly Syntax                                                            | 236  |

|    | 15.3.20.3           | Pseudocode                                                                 | 236  |

|    | 15.3.21 JUN         | MP (reserved)                                                              |      |

|    | 15.3.21.1           | Instruction Encoding                                                       | 236  |

|    | 15.3.21.2           | Assembly Syntax                                                            | 236  |

|    | 15.3.21.3           | Pseudocode                                                                 | 236  |

|    | 15.3.22 JUN         | МРІ                                                                        | 236  |

|    | 15.3.22.1           | Instruction Encoding                                                       | 236  |

|    | 15.3.22.2           | Assembly Syntax                                                            | 237  |

|    | 15.3.22.3           | Pseudocode                                                                 | 237  |

|    | 15.3.23 JLE         |                                                                            | 237  |

|    | 15.3.23.1           | Instruction Encoding                                                       | 237  |

|    | 15.3.23.2           | Assembly Syntax                                                            | 237  |

|    | 15.3.23.3           | Pseudocode                                                                 | 237  |

|    | 15.3.24 JLE         | 1                                                                          | 237  |

|    | 15.3.24.1           | Instruction Encoding                                                       | 237  |

|    | 15.3.24.2           | Assembly Syntax                                                            | 237  |

|    | 15.3.24.3           | Pseudocode                                                                 | 238  |

|    | 15.3.25 IRC         | )                                                                          |      |

|    | 15.3.25.1           | Instruction Encoding                                                       | 238  |

|    | 15.3.25.2           | Assembly Syntax                                                            | 238  |

|    | 15.3.25.3           | Pseudocode                                                                 | 238  |

|    | 15.3.26 R (0        | Only for analog converter)                                                 | 238  |

|    | 15.3.26.1           | Instruction Encoding                                                       | 238  |

|    | 15.3.26.2           | Assembly Syntax                                                            | 238  |

|    | 15.3.26.3           | Pseudocode                                                                 | 238  |

| ©2 | 9 . s reserved by L | inko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xvii |

| 15.3.27    | BREAK(Only for analog converter)               |     |

|------------|------------------------------------------------|-----|

| 15.3.27.   | .1 Instruction Encoding                        | 238 |

| 15.3.27.   | .2 Assembly Syntax                             | 239 |

| 15.3.27.   | .3 Pseudocode                                  | 239 |

| 15.3.28    | END (Only for analog converter)                |     |

| 15.3.28.   | .1 Instruction Encoding                        | 239 |

| 15.3.28.   | .2 Assembly Syntax                             | 239 |

| 15.3.28.   | .3 Pseudocode                                  | 239 |

| 15.4 Appli | ICATION GUIDE                                  | 239 |

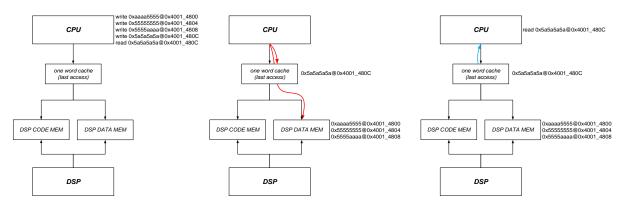

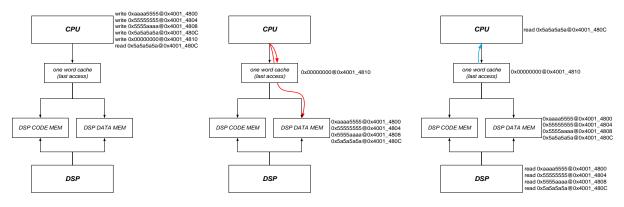

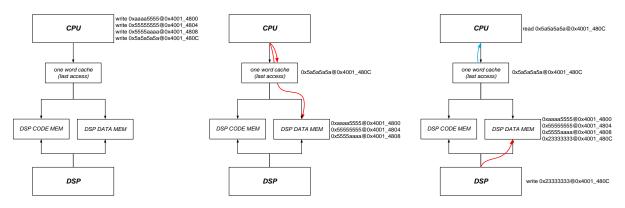

| 15.4.1     | Memory Addressing                              | 239 |

| 15.4.2     | Load after Store                               | 240 |

| 15.4.3     | Delayed Submission of Multi-cycle Instructions | 240 |

| 15.4.4     | Data Filling                                   | 241 |

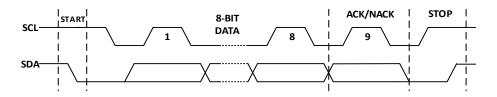

| 16 I2C     |                                                | 243 |

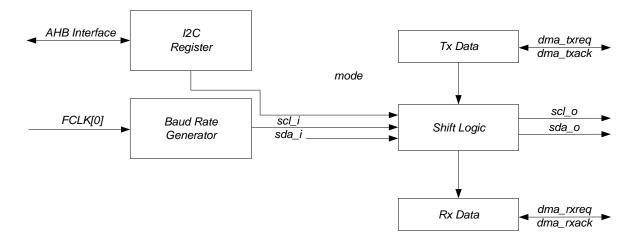

| 16.1 INTRO | DDUCTION                                       | 243 |

| 16.2 MAIN  | I FEATURES                                     | 243 |

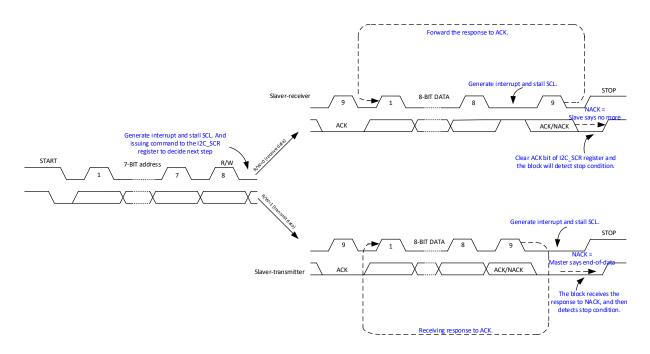

| 16.3 FUNC  | TIONAL DESCRIPTION                             | 243 |

| 16.3.1     | Functional Block Diagram                       | 243 |

| 16.3.2     | Pin Function Description                       | 244 |

| 16.3.2.1   | Mode Selection                                 | 244 |

| 16.3.2.2   | 2 I2C Interface Slave Mode                     | 246 |

| 16.3.2     | 2.2.1 Slave Mode Single-byte Transmission      | 246 |

| 16.3.2     | 2.2.2 Slave Mode Single-byte Transport         | 247 |

| 16.3.2     | 2.2.3 Slave Mode Single-byte Receive           | 247 |

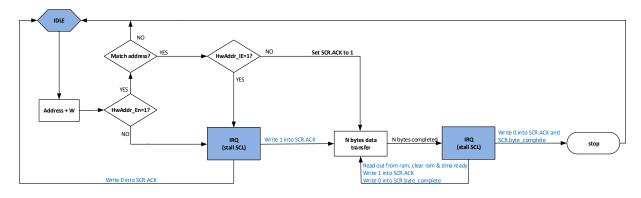

| 16.3.2.3   | Slave Mode DMA Transmission                    | 248 |

| 16.3.2     | 2.3.1 Slave Mode DMA Transport                 | 248 |

| 16.3.2     | 2.3.2 Slave Mode DMA Receive                   | 249 |

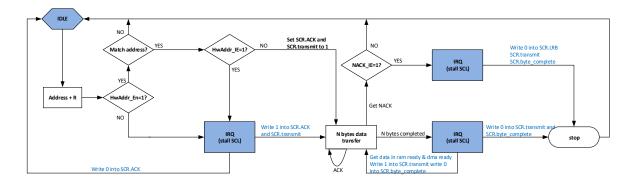

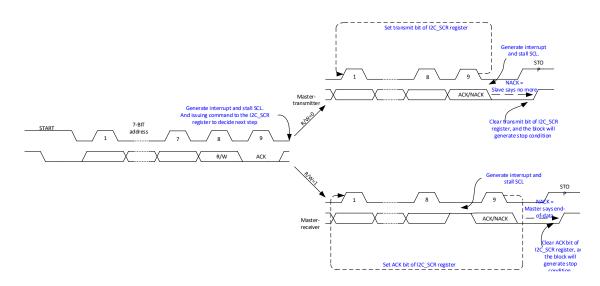

| 16.3.2.4   | I2C Interface Master Mode                      | 249 |

| 16.3.2     | 2.4.1 Master Mode Single-byte Transmission     | 250 |

| 16.3.2     | 2.4.2 Master Mode Single-byte Transport        | 250 |

|            |                                                |     |

©2 Preserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited.

| 16.3.2          | .4.3 Master Mode Single-byte Receive                                           | 251 |

|-----------------|--------------------------------------------------------------------------------|-----|

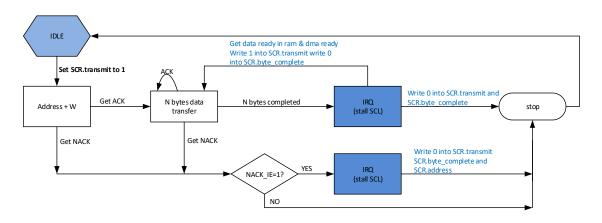

| 16.3.2          | .4.4 Master Mode DMA Transmission                                              | 251 |

| 16.3.2          | .4.5 Master Mode DMA Transport                                                 | 251 |

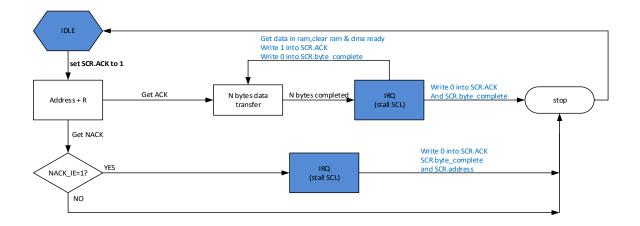

| 16.3.2          | .4.6 Master Mode DMA Receive                                                   | 252 |

| 16.3.2.5        | I2C Bus Exception Handling                                                     | 253 |

| 16.3.2.6        | DMA Transmission                                                               | 253 |

| 16.3.2.7        | MCU Transmission                                                               | 254 |

| 16.3.2.8        | Interrupt Handling                                                             | 254 |

| 16.3.2.9        | Communication Speed Setting                                                    | 255 |

| 16.4 Regist     | rer                                                                            | 255 |

| 16.4.1          | Address Allocation                                                             |     |

| 16.4.2          | Register Description                                                           |     |

| 16.4.2.1        | Address Register (I2C0_ADDR)                                                   | 256 |

| 16.4.2.2        | System Control Register (I2C0_CFG)                                             | 256 |

| 16.4.2.3        | Status Control Register (I2C0_SCR)                                             | 257 |

| 16.4.2.4        | Data Register (I2C0_DATA)                                                      | 258 |

| 16.4.2.5        | Main Mode Register (I2C0_MSCR)                                                 | 259 |

| 16.4.2.6        | DMA Transmission Control Register (I2C0_BCR)                                   |     |

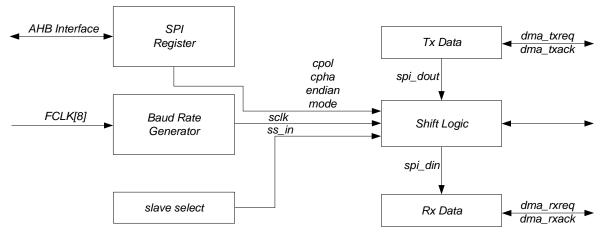

| 17 SPI          |                                                                                | 261 |

| 17.1 INTRO      | DUCTION                                                                        |     |

| 17.2 MAIN       | Features                                                                       | 261 |

| 17.3 FUNCT      | IONAL DESCRIPTION                                                              |     |

| 17.3.1          | Functional Block Diagram                                                       |     |

| 17.3.2          | Pin Function Description                                                       |     |

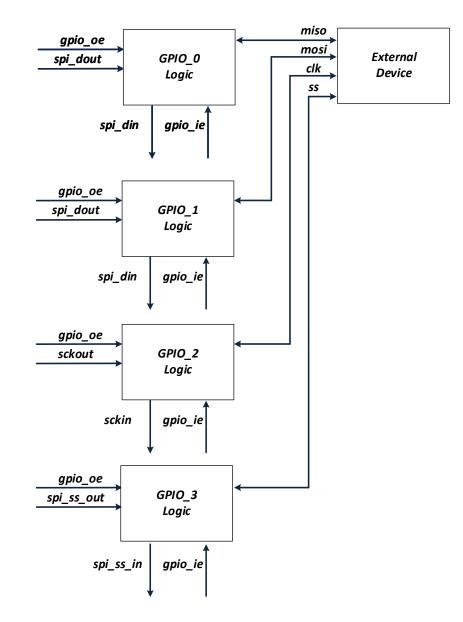

| 17.3.2.1        | Full-duplex Mode                                                               | 262 |

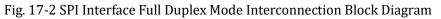

| 17.3.2.2        | Half-duplex Mode                                                               |     |

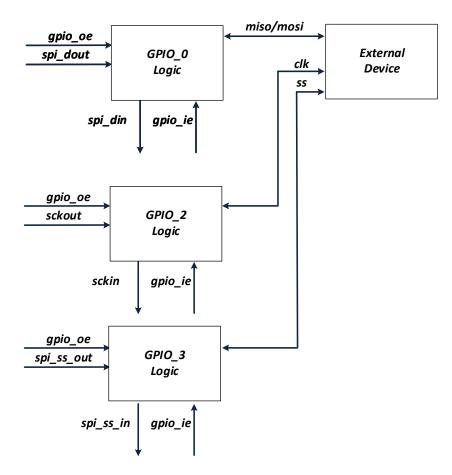

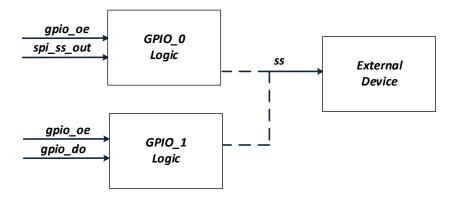

| 17.3.2.3        | Chip Select Signal                                                             |     |

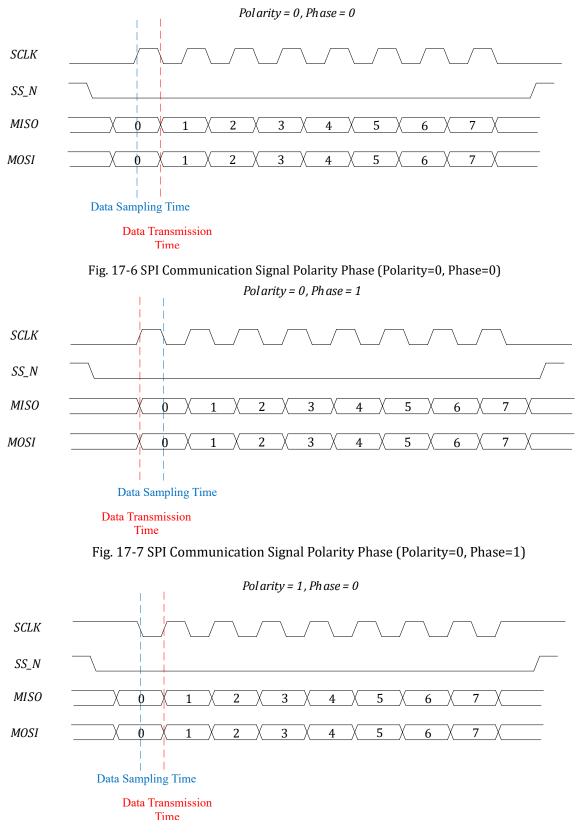

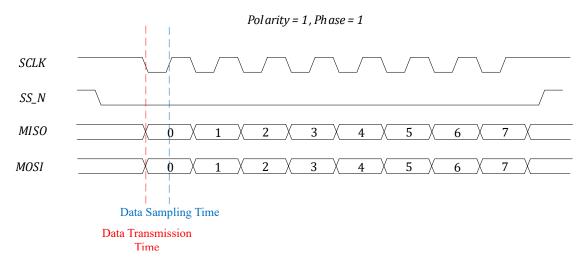

| 17.3.2.4        | Communication Format                                                           |     |

| 17.3.2.5        | Data Format                                                                    |     |

| 17.3.2.6        | DMA Transmission                                                               |     |

| ©2 9 s reserved | by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xix |

| 17.3.2.7 MCU Transmission                           |     |

|-----------------------------------------------------|-----|

| 17.3.2.8 External Event Transmission                |     |

| 17.3.2.9 Interrupt Handling                         |     |

| 17.3.2.10 Baud Rate Setting                         |     |

| 17.4 Register                                       | 269 |

| 17.4.1 Address Allocation                           |     |

| 17.4.2 System Control Register (SPI_CFG)            |     |

| 17.4.3 Interrupt Register (SPI_IE SPI)              |     |

| 17.4.4 Baud Rate Setting Register (SPI_DIV)         | 272 |

| 17.4.5 SPI Transmit Data Register (SPI_TX_DATA)     | 272 |

| 17.4.6 SPI Receive Data Register (SPI_RX_DATA)      |     |

| 17.4.7 SPI Transfer Data Length Register (SPI_SIZE) |     |

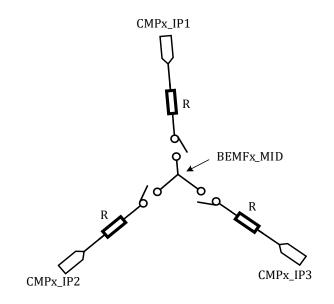

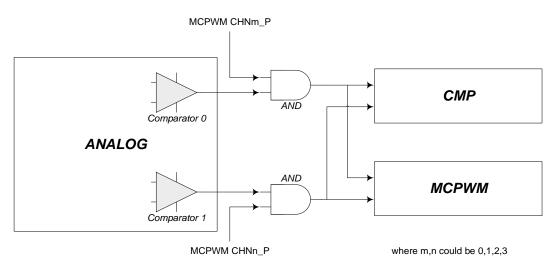

| 18 CMP                                              | 274 |

| 18.1 INTRODUCTION                                   | 274 |

| 18.2 Register                                       | 276 |

| 18.2.1 Address Allocation                           |     |

| 18.2.2 Register Description                         |     |

| 18.2.2.1 CMP_IE                                     |     |

| 18.2.2.2 CMP_IF                                     |     |

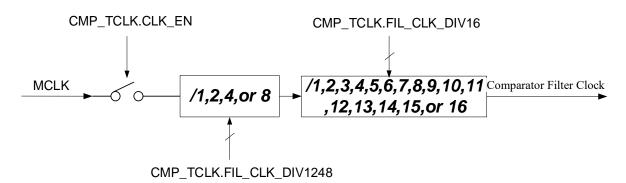

| 18.2.2.3 CMP_TCLK                                   | 277 |

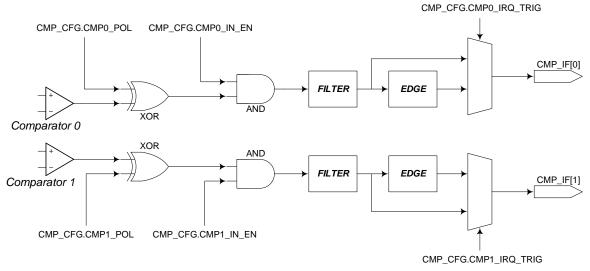

| 18.2.2.4 CMP_CFG                                    | 278 |

| 18.2.2.5 CMP_BLCWIN                                 |     |

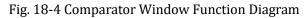

| 19 CAN                                              | 282 |

| 19.1 INTRODUCTION                                   |     |

| 19.1 Main Features                                  |     |

| 19.2 FUNCTIONAL DESCRIPTION                         |     |

| 19.2.1 Functional Block Diagram                     |     |

| 19.2.2 Pin Function Description                     |     |

| 19.2.2.1 Operating Mode                             |     |

| 19.2.2.2 DMA Transmission                           |     |

|                                                     |     |

| 19.2.2.3       | MCU Transmission                                                                 | 284 |

|----------------|----------------------------------------------------------------------------------|-----|

| 19.2.2.4       | Interrupt Handling                                                               | 284 |

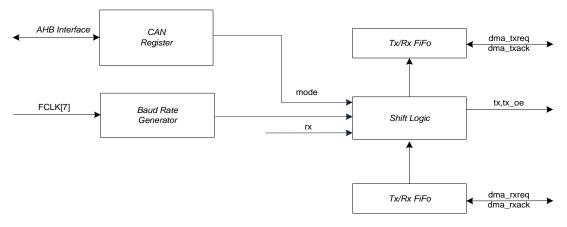

| 19.2.2.5       | Communication Sampling Settings                                                  | 284 |

| 19.2.2.6       | D Filtering                                                                      | 285 |

| 19.2.2.7       | ' Send Frame Format                                                              | 287 |

| 19.2.2.8       | 8 Receive Frame Format                                                           | 288 |

| 19.2.2.9       | Send                                                                             | 289 |

| 19.2.2.10      | 0 Receive                                                                        | 290 |

| 19.2.3 I       | Register                                                                         | 290 |

| 19.2.3.1       | Address Allocation                                                               | 290 |

| 19.2.3.2       | 2 Register Description                                                           | 291 |

| 19.2.3         | 3.2.1 Mode Register (CAN_MOD)                                                    | 291 |

| 19.2.3         | 3.2.2 Command Register (CAN_CMR)                                                 | 292 |

| 19.2.3         | 3.2.3 Status Register (CAN_SR)                                                   | 293 |

| 19.2.3         | 3.2.4 Interrupt Status Register (CAN_IR)                                         | 294 |

| 19.2.3         | 3.2.5 Interrupt Control Register (CAN_EIR)                                       | 294 |

| 19.2.3         | 3.2.6 Baud Rate 0 Control Register (CAN_BTR0)                                    | 295 |

| 19.2.3         | 3.2.7 Baud Rate 0 Control Register (CAN_BTR1)                                    | 296 |

| 19.2.3         | 3.2.8 Arbitration Lost Capture Register (CAN_ALC)                                | 296 |

| 19.2.3         | 3.2.9 Error Code Capture Register (CAN_ECC)                                      | 297 |

| 19.2.3         | 3.2.10 Error & Warning Threshold Register (CAN_EWLR)                             | 298 |

| 19.2.3         | 3.2.11 Receive Error Counter Register (CAN_RXERR)                                | 298 |

| 19.2.3         | 3.2.12 Transmit Error Counter Register (CAN_TXERR)                               | 299 |

| 19.2.3         | 3.2.13 Transceiver Register (AN_TXRX0~ CAN_TXRXC)                                | 299 |

| 19.2.3         | 3.2.14 ID Register (CAN_ACR)                                                     |     |

| 19.2.3         | 3.2.15 ID Mask Register (CAN_AMR)                                                |     |

| 19.2.3         | 3.2.16 FIFO Effective Receive Data Register (CAN_RMC)                            |     |

| 19.2.3         | 3.2.17 Effective Receive Data Address Register (CAN_RBSA)                        |     |

| 19.2.3         | 3.2.18 Clock Divider Register (CAN_CDR)                                          |     |

| 19.2.3         | 3.2.19 RX FIFO Register (CAN_ RFIFO0 ~ CAN_RFIFO31)                              |     |

| 9 s reserved l | d by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | xxi |

|     | 19.2    | .2.3.2.20 TX FIFO Register (CAN_TFIFO0 ~ CAN_TFIFO12) |  |

|-----|---------|-------------------------------------------------------|--|

| 20  | SIF     |                                                       |  |

| 20. | 1 Intr  | FRODUCTION                                            |  |

| 20. | 2 Mai   | ain Features                                          |  |

| 20. | 3 Fun   | NCTIONAL DESCRIPTION                                  |  |

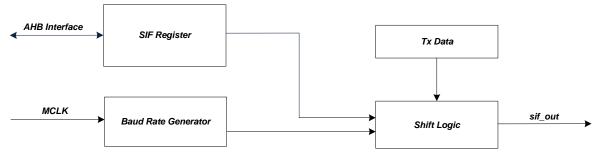

| ź   | 20.3.1  | Functional Block Diagram                              |  |

| ź   | 20.3.2  | Pin Function Description                              |  |

| ź   | 20.3.3  | Mode Selection                                        |  |

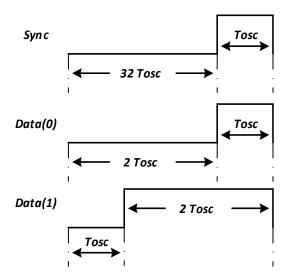

| ź   | 20.3.4  | SIF Interface Transmission                            |  |

| ź   | 20.3.5  | Interrupt Handling                                    |  |

| ź   | 20.3.6  | Communication Speed Setting                           |  |

| 20. | 4 Regi  | GISTER                                                |  |

| ź   | 20.4.1  | Address Allocation                                    |  |

| ź   | 20.4.2  | Register Description                                  |  |

|     | 20.4.2. | 2.1 Configuration Register (SIF_CFG)                  |  |

|     | 20.4.2. | 2.2 Baud Rate Register (SIF_FREQ)                     |  |

|     | 20.4.2. | 2.3 Status Control Register (SIF_IRQ)                 |  |

|     | 20.4.2. | 2.4 Data Register (SIF_WDATA)                         |  |

| 21  | WATC    | CHDOG                                                 |  |

| 21. | 1 Intr  | FRODUCTION                                            |  |

| 21. | 2 Regi  | GISTER                                                |  |

| Ź   | 21.2.1  | Address Allocation                                    |  |

| ź   | 21.2.2  | Register Description                                  |  |

|     | 21.2.2. | 2.1 Watchdog Clear Register (SYS_WDT_CLR)             |  |

| 22  | VERSI   | SION HISTORY                                          |  |

LKS32MC08x User Manual

## **List of Tables**

| Table 2-1 System Address Space Allocation                                 | 3  |

|---------------------------------------------------------------------------|----|

| Table 3-1 Interrupt Number List                                           | 4  |

| Table 5-1 System Clock Source                                             | 14 |

| Table 5-2 Frequency Division Configuration When PLL is Used as MCLK Clock | 15 |

| Table 5-3 Hardware Reset Source                                           | 19 |

| Table 5-4 System Control Register                                         | 21 |

| Table 5-5 Comparator output register                                      | 22 |

| Table 5-6 AFE Register 0 (SYS_AFE_REG0)                                   | 22 |

| Table 5-7 AFE Register 1 (SYS_AFE_REG1)                                   | 24 |

| Table 5-8 AFE Register 2 (SYS_AFE_REG2)                                   | 25 |

| Table 5-9 AFE Register 3 (SYS_AFE_REG3)                                   | 25 |

| Table 5-10 AFE Register 4 (SYS_AFE_REG4)                                  | 27 |

| Table 5-11 AFE Register 5 (SYS_AFE_REG5)                                  | 28 |

| Table 5-12 AFE Register 6 (SYS_AFE_REG6)                                  | 29 |

| Table 5-13 AFE Register 7 (SYS_AFE_REG7)                                  |    |

| Table 5-14 DAC Digital Register (SYS_AFE_DAC)                             | 31 |

| Table 5-15 Clock Control Register (SYS_CLK_CFG)                           |    |

| Table 5-16 Reset Control Register (SYS_RST_CFG)                           |    |

| Table 5-17 Reset Source Record Register (SYS_RST_SRC)                     |    |

| Table 5-18 Reset Source Record Clear Register (SYS_CLR_RST)               | 33 |

| Table 5-19 Peripheral Clock Divider Register 0 (SYS_CLK_DIV0)             | 34 |

| Table 5-20 Peripheral Clock Divider Register 2 (SYS_CLK_DIV2)             | 34 |

| Table 5-21 Peripheral Clock-Gating Register (SYS_CLK_FEN)                 | 35 |

| Table 5-22 Sleep Register (SYS_CLK_SLP)                                   | 35 |

| Table 5-23 Correction Mode Register (SYS_TRIM)                            |    |

| Table 5-24 Soft Reset Register (SYS_SFT_RST)                              |    |

| Table 5-25 Write Protection Register (SYS_WR_PROTECT)                     |    |

| Table 5-26 DAC Gain Correction Register (SYS_AFE_DAC_AMC)                 |    |

| Table 5-27 DAC DC Offset Register (SYS_AFE_DAC_DC)                          |    |

|-----------------------------------------------------------------------------|----|

| Table 6-1 LASH Access Space Allocation                                      |    |

| Table 6-2 FLASH Sector Address Allocation                                   |    |

| Table 6-3 Register Description of IAP VTOR                                  |    |

| Table 6-4 List of FLASH Controller Register                                 |    |

| Table 6-5 FLASH_CFG Configuration Register                                  |    |

| Table 6-6 Address Register (FLASH_ADDR)                                     |    |

| Table 6-7 Write Register (FLASH_WDATA)                                      |    |

| Table 6-8 Read Register (FLASH_RDATA)                                       |    |