# LKS32MC07X with built-in 3P3N driver Datasheet

© 2023, all rights reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited.

${\small @ 2023 All rights reserved by Linko Semiconductor. Confidential. Unauthorized dissemination is prohibited. }$

# **1** Overview

### **1.1 Functions**

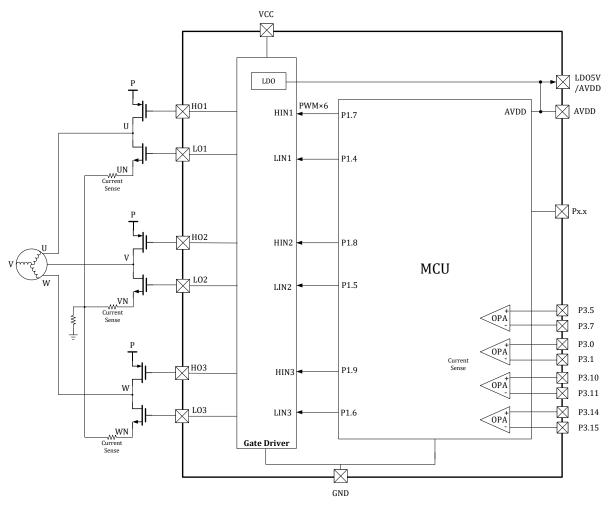

LKS32MC074F/076F is a 32-bit MCU targeting motor control applications. With all modules required for common motor control systems and three-phase P/N MOS gate driver, it can directly drive three-channel P/N MOS power device.

• Features

- > 96MHz 32-bit Cortex-M0 core

- > Customized instruction set DSP for motor control

- Ultra low power sleep mode

- > Three-phase full-bridge bootstrap gate driver

- Industrial temperature range

- ▶ High ESD and group pulse reliability

#### • Memory

- ▶ Built-in flash including 64kB/128kB main area and 1.5kB NVR

- Endurance: 100,000 Cycles(min)

- > Data retention: more than 100 years under room temperature 25 °C

- Single byte program: 7.5us(max), Sector erase: 5ms(max)

- Sector size 512bytes, supporting Sector erase/program

- Flash data anti-theft by programming the last word of flash to any words other than 0xFFFFFFFF

#### • Operating Conditions

- 7.5~32V (Maximum: 40V), single power supply, with an integrated internal 5V LDO for partial power supply for internal MCU of chip

- ➢ Operating Conditions: -40∼105°C

- Clock

- ▶ 8MHz built-in high-precision RC oscillator, with an accuracy of ± 1% at -40 ~ 105 °C

- > 32KHz built-in low-speed clock for low-power mode

- > Operating on an external 8MHz crystal is available

- ▶ Internal PLL up to 96 MHz

- Peripheral module

- Two UARTs

- > Two 16-bit standard timers (TIM), support capture and edge-aligned PWM function

- Two 32-bit standard timers (TIM), support capture and edge-aligned PWM function; support orthogonal code input, CW/CCW input, and pulse&symbol input

- Motor control PWM module, supports 12 channels/6 pairs of PWM waveform output, inde-

pendent dead-band control

- > Hall signal interface with speed measurement and debouncing function

- Hardware watchdog

- 4 Groups of 16bit GPIO at the most. 8 GPIOs could be used as wake-up source,15 GPIOs could be used as external IRQ source

#### • Simulation module

- Two 12bit SAR ADC, simultaneous double sampling, 3Msps sampling and conversion rate, and each sampling circuit supports up to 16 channels, including 4 OPA outputs and 10 ex-ternal ADC channels for a total of 14 optional ADC channel signals

- > Four operational amplifiers. Differential PGA mode is available.

- > Three comparators. Hysteresis mode is available.

- > Two 12bit digital-to-analog converter (DAC)

- ➤ ± 2 °C built-in temperature sensor

- > 1.2V 0.8% built-in linear regulator

- Low-power LDO and power monitoring circuit

- > RC oscillator with high precision and low temperature drift

- Crystal oscillator circuits

- ➢ Integrated 32kHz+4MHz RC

- ➢ Integrated 96MHz PLL

## **1.2 Performance advantages**

- > High reliability, high integration level, small package size, saving BOM cost;

- Integrated 4 channels high-speed OPAs and 3 channels comparators, meeting the needs of different system topology like single resistance/double resistance/three resistance current sampling;

- High-speed OPA is integrated with over-voltage protection circuit, which allows high-voltage common-mode signals to be input, which could support direct current sampling of MOSFET resistance with the simplest circuit topology.

- Via a proprietary technique, ADC and high-speed OPA could cooperate well, making them able to handle a wider current dynamic range, while ensuring the sampling precision of high-speed small current and low-speed high current;

- The control circuit is simple and efficient, with strong anti-interference ability, stable and reliable;

- Single power 7.5~32V supply, integrated 5V LDO internally;

- > Three-phase full-bridge bootstrap gate driver is integrated

- Supports IEC/UL60730 functional safety certification

Applicable to control systems such as inductive BLDC/non-inductive BLDC/inductive FOC/non-inductive FOC and stepper motors, permanent magnet synchronous and asynchronous motors.

4

# **1.3 Naming Conventions**

|            | $\underline{LKS32}  \underline{MC}  \underline{070}  \underline{R}  \underline{8}  \underline{T}  \underline{8}  \underline{XX}$ |

|------------|----------------------------------------------------------------------------------------------------------------------------------|

| Device ser | ies                                                                                                                              |

| LKS32      | = 32bit MCU                                                                                                                      |

|            |                                                                                                                                  |

| Product ty |                                                                                                                                  |

| MC         | = Motor Control Applications                                                                                                     |

| AT         | = Automobile Applications                                                                                                        |

| Device sub | family                                                                                                                           |

| 070/071    | = 2.5~5.5V,2 ADC,4 PGA,DSP                                                                                                       |

| 070FL/071  | DO/074D/DO = 2.5~5.5V,2 ADC,4 PGA,DSP,6N Driver                                                                                  |

| 074F/076F  | = 2.5~5.5V,2 ADC,4 PGA,DSP,6N Driver                                                                                             |

| 072        | = 2.5~5.5V,2 ADC,3 PGA                                                                                                           |

| 073        | = 2.5~5.5V,2 ADC,1 PGA                                                                                                           |

| 077        | = 2.5~5.5V,2 ADC,2 PGA                                                                                                           |

| 077E       | = 7.5~28V, 2 ADC, 2 PGA, 3P3N Driver                                                                                             |

|            |                                                                                                                                  |

| Pin count  |                                                                                                                                  |

| L          | = 16 pins                                                                                                                        |

| Н          | = 20 pins                                                                                                                        |

| М          | = 24 pins                                                                                                                        |

| К          | = 32 pins                                                                                                                        |

| F          | = 40 pins                                                                                                                        |

| C          | = 48 pins                                                                                                                        |

| N          | = 52 pins                                                                                                                        |

| R          | = 64 pins                                                                                                                        |

| V          | =100 pins                                                                                                                        |

| v<br>Z     | =144 pins                                                                                                                        |

|            |                                                                                                                                  |

| Code size  |                                                                                                                                  |

| 4          | = 16Kbyte Flash Memory                                                                                                           |

| 6          | = 32Kbyte Flash Memory                                                                                                           |

| 8          | = 64Kbyte Flash Memory                                                                                                           |

| В          | =128Kbyte Flash Memory                                                                                                           |

| С          | =256Kbyte Flash Memory                                                                                                           |

| D          | =384Kbyte Flash Memory                                                                                                           |

| Е          | =512Kbyte Flash Memory                                                                                                           |

| Package    |                                                                                                                                  |

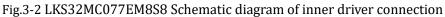

| Р          | = TSSOP                                                                                                                          |

| Т          | = TQFP/LQFP                                                                                                                      |

| Q          | = QFN                                                                                                                            |

| Š          | = SSOP                                                                                                                           |

| Н          | = BGA                                                                                                                            |

| Temperati  |                                                                                                                                  |

| 6          | $= -40 \sim 85^{\circ}$                                                                                                          |

| 8          | $= -40 \sim 105^{\circ}$                                                                                                         |

| 9          | $= -40 \sim 105$<br>= $-40 \sim 125^{\circ}$                                                                                     |

| -          |                                                                                                                                  |

| Options    |                                                                                                                                  |

| TR         | = Tape and reel packing                                                                                                          |

| Р          | = Engineering Samples                                                                                                            |

## Fig.1-1 Naming Conventions of Linko Components

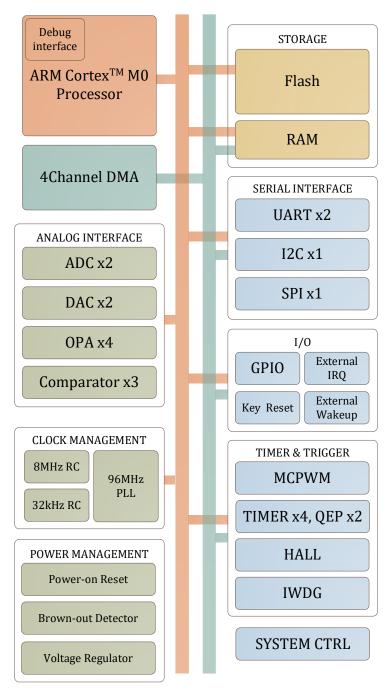

## **1.4 Resource Diagram**

Fig. 1-2 LKS32MC07x Resource Diagram

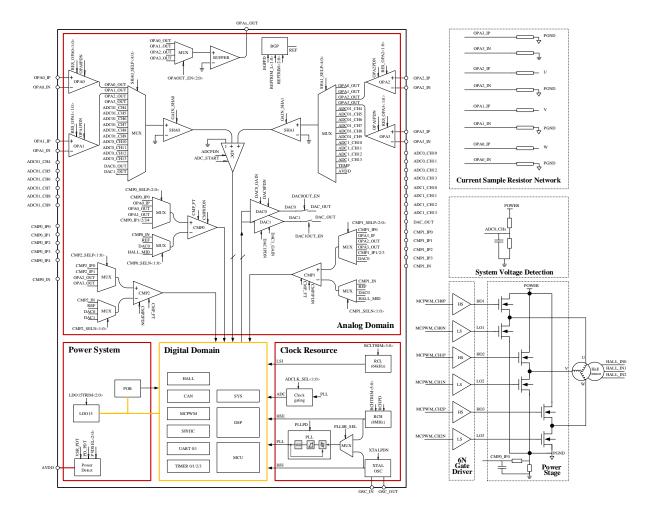

# 1.5 FOC System Example

\* ADC 01 \_ CH4  $\sim$  ADC 01 \_ CH9 are common channels for ADC0 and ADC 1

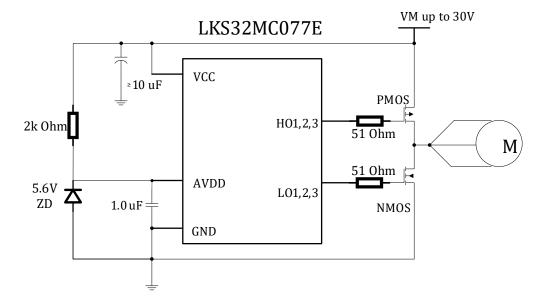

Fig.1-3 LKS32MC077EM6S8 Simplified Schematic of FOC System

#### Device selection table

# 2 Device selection table

|                  | Frequency (MHz) | Flash (kB) | RAM (kB) | ADC ch. | DAC     | Comparator | Comparator ch. | OPA | HALL | IdS | IIC | UART | CAN | Temp. Sensor | PLL | QEP | Gate driver | Gate Driver current (A) | Pre-drive supply (V) | Gate floating voltage (V) | Others | Package         |

|------------------|-----------------|------------|----------|---------|---------|------------|----------------|-----|------|-----|-----|------|-----|--------------|-----|-----|-------------|-------------------------|----------------------|---------------------------|--------|-----------------|

| LKS32MC070FLRBT8 | 96              | 128        | 12       | 14      | 12BITx2 | 3          | 10             | 4   | 3    | 1   | 1   | 2    | Yes | Yes          | Yes | Yes | 6N          | +1/-1                   | 4.5~20               | 250                       | 5V LDO | LQFP64          |

| LKS32MC070RBT8   | 96              | 128        | 12       | 14      | 12BITx2 | 3          | 11             | 4   | 3    | 1   | 1   | 2    | Yes | Yes          | Yes | Yes |             |                         |                      |                           |        | LQFP64          |

| LKS32MC071CBT8   | 96              | 128        | 12       | 13      | 12BITx2 | 3          | 11             | 4   | 3    | 1   | 1   | 2    | Yes | Yes          | Yes | Yes |             |                         |                      |                           |        | TQFP48          |

| LKS32MC071C8T8   | 96              | 64         | 12       | 13      | 12BITx2 | 3          | 11             | 4   | 3    | 1   | 1   | 2    |     | Yes          | Yes | Yes |             |                         |                      |                           |        | TQFP48          |

| LKS32MC071D0C8T8 | 96              | 64         | 12       | 13      | 12BITx2 | 3          | 10             | 3   | 3    | 1   | 1   | 2    | Yes | Yes          | Yes | Yes | 6N          | +1/-1                   | 4.5~20               | 250                       | 5V LDO | TQFP48          |

| LKS32MC072KBQ8   | 96              | 128        | 12       | 8       | 12BITx2 | 3          | 7              | 3   | 3    | 1   | 1   | 2    |     | Yes          | Yes | Yes |             |                         |                      |                           |        | QFN5*5 32L-0.75 |

| LKS32MC072KBT8   | 96              | 128        | 12       | 9       | 12BITx2 | 2          | 5              | 0   | 3    | 1   | 1   | 2    | Yes | Yes          | Yes | Yes |             |                         |                      |                           |        | LQFP32          |

| LKS32MC073HBQ8   | 96              | 128        | 12       | 4       | 12BITx2 | 2          | 4              | 1   | 3    | 0   | 1   | 2    |     | Yes          | Yes | Yes |             |                         |                      |                           |        | QFN3*3 20L-0.75 |

| LKS32MC074DF8Q8  | 96              | 64         | 12       | 13      | 12BITx2 | 3          | 9              | 3   | 3    | 1   | 1   | 2    |     | Yes          | Yes | Yes | 6N          | +1.2/-1.5               | 7~20                 | 200                       |        | QFN5*5 40L-0.75 |

| LKS32MC074D0F8Q8 | 96              | 64         | 12       | 12      | 12BITx2 | 3          | 9              | 3   | 3    | 1   | 1   | 2    |     | Yes          | Yes | Yes | 6N          | +1/-1                   | 4.5~20               | 250                       | 5V LDO | QFN5*5 40L-0.75 |

| LKS32MC076FNBQ8  | 96              | 128        | 12       | 12      | 12BITx2 | 3          | 11             | 4   | 3    | 1   | 1   | 2    | Yes | Yes          | Yes | Yes | 6N          | +1.2/-1.5               | 7~20                 | 200                       |        | QFN52           |

| LKS32MC077MBS8   | 96              | 64         | 12       | 6       | 12BITx2 | 3          | 6              | 2   | 3    | 1   | 1   | 2    |     | Yes          | Yes | Yes |             |                         |                      |                           |        | SSOP24L         |

| LKS32MC077EM8S8  | 96              | 64         | 12       | 6       | 12BITx2 | 3          | 7              | 2   | 3    | 1   | 1   | 2    |     | Yes          | Yes | Yes | 3P3N        | +0.05/-0.3              | 7~32                 |                           | 5V LDO | SSOP24L         |

#### Table 2-1 LKS07x Series Device Selection Table

# 3 Pin Assignment

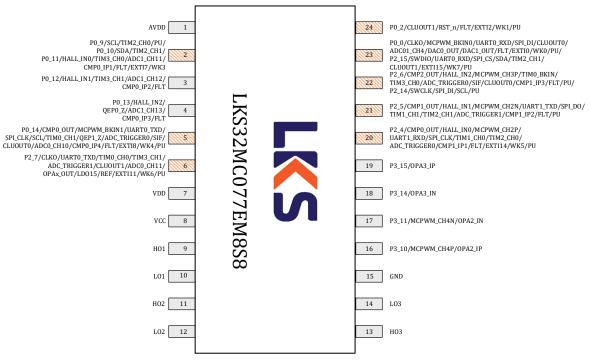

#### 3.1 Pin Assignment and Pin Function Description

#### 3.1.1 Special instructions

The red pin in the pin assignment figures below has built-in pull-up resistors: RSTN has a 100k $\Omega$ built-in pull-up resistor, which is enabled automatically after power-up. SWDIO/SWCLK has a 10k $\Omega$  built-in pull-up resistor, which is enabled automatically after power-up. The remaining red pins have 10k $\Omega$  built-in pull-up resistors, which could be software-enabled.

UARTx\_TX(RX): UART TX and RX support interchange. When the second function of GPIO is selected as UART, and GPIO\_PIE is input enabled, it can be used as UART\_RX; when GPIO\_POE is enabled, it can be used as UART\_TX. Generally, the same GPIO does not enable input and output at the same time, otherwise the input PDI will receive the data sent by the PDO.

SPI\_DI(DO): The DI and DO of SPI can also be interchanged. When the second function of GPIO is SPI, and GPIO\_PIE is input enable, it can be used as SPI\_DI; when GPIO\_POE is output enable, it can be used as SPI\_DO. Generally, the same GPIO does not enable input and output at the same time, otherwise the input PDI will receive the data sent by the PDO.

#### 3.1.2 LKS32MC077EM8S8

Notice: Do not pull up the LDO before the VCC is powered on. Otherwise, the LDO may fail to start after the VCC is powered on.

|   |           | 1                                                                 |

|---|-----------|-------------------------------------------------------------------|

| 1 | AVDD      | Chip power supply, power supply range $2.5 \sim 5.5 V$            |

|   | P0_9      | P0.9                                                              |

|   | SCL       | I2C clock                                                         |

|   | TIM2_CH0  | Timer2 channel 0                                                  |

|   | PU        | Built-in $10k\Omega$ pull-up resistor, software can be turned off |

|   | P0_10     | P0.10                                                             |

|   | SDA       | I2C data                                                          |

| 2 | TIM2_CH1  | Timer2 channel 1                                                  |

| 2 | P0_11     | P0.11                                                             |

|   | HALL_IN0  | HALL interface input 0                                            |

|   | TIM3_CH0  | Timer3 channel 0                                                  |

|   | ADC1_CH11 | ADC1 Channel 11                                                   |

|   | CMP0_IP1  | Comparator 0 positive input 1                                     |

|   | FLT       | IO filtering                                                      |

|   | EXTI7     | External GPIO Interrupt Signal 7                                  |

| Table 3-1 | LKS32MC07 | 7EM8S8 Pin | Function | Description |

|-----------|-----------|------------|----------|-------------|

|           |           |            |          |             |

| Number of program           P0.12         P0.12           RALLINI         HALL interface input 1           TM3_CH1         Timer3 channel 1           ADC1_CH122         ADC1 Channel 12           CMP0_IP2         Comparator 0 positive input 2           PUT         10 filtering           P0.13         P0.13           HALLIN2         HALL interface input 2           QPP0_7         QPD Rooder Phase 7           ADC1_CH13         ADC1 Channel 13           CMP0_IP3         Comparator 0 positive input 3           FUT         10 filtering           FUT         Serial port 0 send (receive)           SPLCLK         SPL dock           SPL         SPL           GPT         Phace Z of GPL 1 encoder           SPL         Singe line communication           CLUOUT0         CLUO output           ADOC CH10         ADOC Channel 10           CMP0_JPL<                                                                               |   | WK3          | External wake-up signal 3                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|--------------------------------------------|

| Hull INI         HALL INI           Hull INI         HALL INI           Hull INI         Hull Initerface input 1           TIM3_CIII         Timer3 channel 12           ACIC_H12         ADCI Channel 12           CMP0_JP2         Comparator 0 positive input 2           HIT         IO filtering           P0_13         P0.13           HALL INTERFace input 2           ADCI_CIII3         ADCI Channel 13           CMP0_JP3         Comparator 0 positive input 3           FLT         IO filtering           VP14         P0.14           CMP0_UDT         Comparator 0 Output           MCPWM, BKIN1         PWM Shutdown Input Signal 1           UARD_TXD         Serial port 0 send (receive)           SILLK         SPI clock           SILLK         SPI clock           TIM0_CII1         Timer0 channel 1           QEP1_Z         Phase Z of QEP1 encoder           SIF         Single line communication           CUUTO         CUD output           ADC_CIRIO         ADC0 channel 10           CMP0_IP4         Comparator 0 positive input 4           PLT         Io filtering           FIT         Io filtering           Extrand QPD                                            |   | _            |                                            |

| 3TIM3_CH1Timer3 channel 1ADC1_CH12ADC1 Channel 12MP0_IP2Comparator 0 positive input 2PLT10 filteringPLT10 filteringHALL_INZHALL interface input 2QEP0_ZQEP0 Encoder Phase ZADC1_CH13ADC1 Channel 13CMP0_IP3Comparator 0 positive input 3FI.T10 filteringP0_14P0.14CMP0_UTCComparator 0 outputCMP0_UTCComparator 0 OutputCMP0_UTCSerial port 0 send (receive)SP1_CLKSP1 dockSCL12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderSIFSingle line communicationCLIOUTOCLIO Outpiger signal output (for debugging)SIFSingle line communicationCLIOUTOCLUO outputADC_CH10ADC Channel 10CMP0_IP4Comparator 0 positive input 4PUBuilt-in 10K pull-up resistor, software switchablePUBuilt-in 10K pull-up resistor, s                                                                                                   |   |              |                                            |

| A<br>A<br>ADC1 CH12ADC1 Channel 12CMP0.JP2Comparator 0 positive input 2FLTI0 filteringFLTI0 filteringP0.13P0.13HALL,N2HALL interface input 2QEP0.C.QEP0 Encoder Phase Z.ADC1,CH13ADC1 Channel 13CMP0.P3Comparator 0 positive input 3FLTI0 filteringP0.14P0.14CMP0.UTComparator 0 outputMCPWM,BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SF1CLKSP1 ClockSCL12 C clockTIM0.CH1Timer0 channel 1QEP1.ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLU0UTOCLU0 outputADC_CTI10ADC0 Channel 10CMP0.JP4Comparator 0 positive input 4FLTI0 filteringEXTBExternal wake-up signal 8WK4External wake-up signal 4PUWIA1+ in 10K1 pull-up resistor, software switchablePUBuilt-in 10K1 pull-up resistor, software switchablePUSifiltTimer0 channel 1ADC0.CH11ADC1 Channel 1.ADTCock output (for debugging)GLK0Cock output (for debugging)GLK0Cock output (for debugging)GLK0Cock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0.CH0Timer0 channel 1ADC1.RIGGER1ADC1 trigger signa                                                                                                                                  |   |              | -                                          |

| CMP0.JP2Comparator 0 positive input 2FLT10 filteringFLT10 filteringP0.13P0.13HALL INEHALL interface input 2QEP0.ZQEP0 Encoder Phase ZADC1_CH13ADC1 Channel 13CMP0.JP3Comparator 0 positive input 3FLT10 filteringP0.14P0.14CMP0_OUTComparator 0 outputMCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPL_CLKSPI clockSCL12 CclockTM0_CH1Timer0 channel 1QEP1.ZPhase Z of QEP1 encoderSFSingle line communicationCLUOUTOCLUO outputADC_TRIGGER0ADC0 trigger signal output (for debugging)SFSingle line communicationCLUOUTOCLUO channel 10CM0_CH11Dinterrupt Signal 8WK4External wake-up signal 4PUBuilt-in 104R pul-lup resistor, software switchablePUBuilt-in 104R pul-lup resistor, software switch                                    | 3 |              |                                            |

| FLTIO filteringP0_13P0.13HALL_INZHALL interface input 2QEP0.Z.QEP0 Encoder Phase Z.ADC1_CI113ADC1 Channel 13CMP0_P3Comparator 0 positive input 3FLTIO filteringP0_14P0.14CMP0_OUTComparator 0 OutputMCPWM_BKIN1PVM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPL_CLKSPI clockSCI.12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSing line communicationCLUOUTOCLU0 outputADC0_CH10ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringFLTIO filteringFLTIO filteringSIFExternal GPIO Interrupt Signal 8WK4External GPIO Interrupt Signal 8WK4External output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)LART0_TXDSerial port 0 send (receive)TIM0_CH1Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)ADC_TRIGGER1ADC1 trigg                                                                                           |   |              |                                            |

| P0.13P0.13IALL.IN2IIALL interface input 2QEP0_ZQEP0 Encoder Phase ZAAC1_CH13ADC1 Chnnel 13CMP0_IP3Comparator 0 positive input 3FLTIO filteringP0.14P0.14CMP0_UUTComparator 0 OutputMCPVM_EKIN1PVM Shutdown Input Signal 1MART0_TXDSerial port 0 send (receive)SPL_CLKSPL clockSCL12C clockTIM0_CH1Timer 0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingel line communicationCLU00T0CLU0 outputADC0_CH10ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringFLTIO filteringFLT                                                                                                                                                                                                                                                                                                                  |   |              |                                            |

| Ind.L.IN2IIALL interface input 2QEP0_ZQEP0 Encoder Phase ZADC1_CH13ADC1 Channel 13CMP0_JP3Comparator 0 positive input 3FLTI0 filteringP0_14P0.14CMP0_OUTComparator 0 OutputMCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPLCLKSPL cockSCLI2C clockTIM0_CH1Timer 0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLU00T0CLU0 outputADC_CN10ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FUTI0 filteringFUTI0 filteringEXTR8External GP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchableFUClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC_TRIGGER1ADC1 trigger signal output (for debugging)<                                                                |   |              |                                            |

| 4QEP0.ZQEP0 Encoder Phase ZADC1_CH13ADC1 Channel 13CMP0_IP3Comparator 0 positive input 3FLT10 filteringP0_14P0.14CMP0_OUTComparator 0 OutputMCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPI_CLKSPI clockSCL12C clockTIM0_CH1Timer 0 channel 1QEP1_ZPhase Z of QEP1 encoderQEP1_ZPhase Z of QEP1 encoderSIFSingle line communicationCLU0UT0CLU0 outputADC0_CRIGER0ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FUT10 filteringEXT18External GPI0 Interrupt Signal 8WK4External QAU-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchableTIM3_CH1Timer 0 channel 1ADC1_TRIGER1ADC1 trigger signal output (for debugging)LU01T1CLU1 outputADC1TRIGER1ADC1 trigger signal output (for debugging)CLW0Clock output (for debugging)LU01T1CLU1 outputADC_TRIGER1ADC1 trigger signal output (for debugging)CLW0Clock output (for debugging)CLW0Clock outputADC_TRIGER1ADC1 trigger signal output (for debugging)CLW0CLU01T1CLU1 outputADC2,TRIGER1ADC                                                                                  |   |              |                                            |

| 4         ADC1_CH13         ADC1 Channel 13           CMP0_IP3         Comparator 0 positive input 3           FLT         I0 filtering           P0_14         P0.14           MCPWM_BKIN1         PWM Shutdown Input Signal 1           UART0_TXD         Serial port 0 send (receive)           SPI_CLK         SPI clock           SCL         I2C clock           TIM0_CH1         Timer0 channel 1           QEP1_Z         Phase Z of QEP1 encoder           ADC_TRIGER0         ADC0 trigger signal output (for debugging)           SIF         Single line communication           CLUOUT0         CLU0 output           ADC0_CATIO         ADC0 Channel 10           CMP0_IP4         Comparator 0 positive input 4           FLT         10 filtering           EXT18         External GPI0 Interrupt Signal 8           WK4         External Vake-up signal 4           PU         Built-in 10kΩ pul-up resistor, software switchable           P2_7         P2.7           P2.7         P2.7           CLK0         Clock output (for debugging)           UART0_TXD         Serial port 0 send (receive)           TIM0_CH0         Timer3 channel 1           ADC_TRIGGER1         ADC1 trigg |   |              |                                            |

| CMP0_IP3Comparator 0 positive input 3FLT10 filteringP0_14P0.14CMP0_OUTComparator 0 OutputMCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPLCLKSPL clockSCL12C clockSCL12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUTOCLU0 outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTI0 filteringEXT18External QPI0 Interrupt Signal 8WK4External QPI0 Interrupt Signal 8WK4External QPI0 Interrupt Signal 8VK4External QPI0 To send (receive)TIM0_CH0Timer0 channel 0TIM0_CH1Timer0 channel 1ADC.TRIGER1ADC1 trigger signal output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC.TRIGER1ADC1 trigger signal output (for debugging)CLBOUT1CLU1 outputADC.TRIGER1ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LD0 OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                    | 4 |              |                                            |

| FLTIO filteringPLTIO filteringP0_14P0.14CMP0_OUTComparator 0 OutputMCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPI_CLKSPI clckSPI_CLKSPI clckSCL12C clockTM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLU0UT0CLU0 outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringEXTI8External OPIO Interrupt Signal 8WK4External OPIO Interrupt Signal 8WK4External OPIO Interrupt Signal 9UART0_TXDSerial port 0 send (receive)TM0_CH0Timer0 channel 0TIM0_CH0Timer0 channel 0TIM0_CH0Timer0 channel 0TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLK0Clock output (for debugging)QLART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM0_CH1Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLK0CLK0 Channel 11ADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LDO OutputREFReference VoltageEXT11External GPIO Interrupt Signal 11                                                                                                                                                   |   |              |                                            |

| P0.14P0.14CMP0_OUTComparator 0 OutputMCPWM_BKIN1PVM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPI_CLKSPI_clckSCL12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUTOCLU0 outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLT10 filteringEXT18External GPI0 Interrupt Signal 8WK4External GPI0 Interrupt Signal 4PUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchableTIM0_CH0Timer0 channel 1ADC1_TRIGER1ADC1 trigger signal output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC1_TRIGER1ADC1 trigger signal output (for debugging)ADC1_TRIGER1ADC1 trigger signal output (for debugging)ADC1_TRIGER1ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LD0 OutputREFReference VoltageEXT111External GPI0 Interrupt Signal 11                                                                                     |   |              |                                            |

| CMP0_0UTComparator 0 OutputMCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPL_CLKSPL clockSCL12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUT0CLU0 outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FIT10 filteringEXTI8External GP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kf1 pull-up resistor, software switchablePUBuilt-in 10kf1 pull-up resistor, software switchableVK4External wake-up signal 4PUSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)UART0_TXDSerial port 0 send (receive)TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLIOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LD0 OutputREFReference VoltageEXT111External GP10 Interrupt Signal 11                                                                                                                                                                                                                                                 |   |              |                                            |

| MCPWM_BKIN1PWM Shutdown Input Signal 1UART0_TXDSerial port 0 send (receive)SPLCLKSPL clockSCLI2C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLU0UT0CLU0 outputADC_CH10ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FLTI0 filteringEXT18External QP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10k0 pull-up resistor, software switchableP2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC_TRIGGER1ADC1 trigger signal output (for debugging)ADC_TRIGGER1ADC1 trigger signal output (for debugging)OFA_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                             |   |              |                                            |

| UART0_TXDSerial port 0 send (receive)SPLCLKSPL clockSCLI2C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUT0CLU0 outputADC_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTI0 filteringEXT18External QP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10K0 pull-up resistor, software switchableP2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH111ADC0 channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |              |                                            |

| SPLCLKSPI clockSCL12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUT0CLU0 outputADC_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLT10 filteringEXT18External GPI0 Interrupt Signal 8WK4External GPI0 Interrupt Signal 4PUBuilt-in 10kΩ pul-up resistor, software switchableP2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)ADC_TRIGGER1ADC1 trigger signal output (for debugging)ADC_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |              |                                            |

| ActionCL12C clockTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLU0UT0CLU0 outputADC_CH10ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FLT10 filteringEXT18External GPI0 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchableIMA_C_TRIGGER1ADC1 trigger signal output (for debugging)TIM3_CH1Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC_CH11ADC0 channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |              |                                            |

| FTIM0_CH1Timer0 channel 1QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLU0UT0CLU0 outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringEXT18External GPI0 Interrupt Signal 8WK4External GPI0 Interrupt Signal 4PUBuilt-in 10kΩ pull-up resistor, software switchableVK4External ot enceive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)UURT0_TXDSerial port 0 send (receive)TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC_TRIGGER1ADC0 channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |              |                                            |

| QEP1_ZPhase Z of QEP1 encoderADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUT0CLU0 outputADC0_CH10ADC0 channel 10CMP0_IP4Comparator 0 positive input 4FLTI0 filteringEXTI8External GPI0 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchablePLClck output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LD0 OutputREFReference VoltageEXT11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |              |                                            |

| ADC_TRIGGER0ADC0 trigger signal output (for debugging)SIFSingle line communicationCLUOUT0CLUO outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTI0 filteringEXT18External GP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ pull-up resistor, software switchableVART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LDO OutputREFReference VoltageEXT11External GP10 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |              |                                            |

| SIFSingle line communicationCLUOUTOCLUO outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringEXTI8External GPIO Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchableP2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXT11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 | -            |                                            |

| CLUOUTOCLUO outputADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringEXT18External GPIO Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchablePUBuilt-in 10kΩ comparator 0 send (receive)CLK0Clock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 1ADC1_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXT11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - |              |                                            |

| ADC0_CH10ADC0 Channel 10CMP0_IP4Comparator 0 positive input 4FLTIO filteringEXT18External GP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10k0 pull-up resistor, software switchableP2_7P2.7CLK0Clock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC0_TRIGGER1ADC1 trigger signal output (for debugging)ADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXT11External GP10 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | -            |                                            |

| CMP0_IP4Comparator 0 positive input 4CMP0_IP4Comparator 0 positive input 4FLTIO filteringEXT18External GP10 Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchableP2_7P2.7CLK0Clock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputID0151.5V LDO OutputREFReference VoltageEXT11External GP10 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |              |                                            |

| FLTIO filteringEXT18External GPIO Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchableP2_7P2.7CLK0Clock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXT111External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |              | Comparator 0 positive input 4              |

| EXT18External GPIO Interrupt Signal 8WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchableP2_7P2.7CLK0Clock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLU0UT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputREFReference VoltageEXT111External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |              |                                            |

| WK4External wake-up signal 4PUBuilt-in 10kΩ pull-up resistor, software switchableP2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXTI11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | EXTI8        |                                            |

| PUBuilt-in 10kΩ pull-up resistor, software switchableP2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXTI11External GPI0 Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |              |                                            |

| P2_7P2.7CLKOClock output (for debugging)UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | PU           |                                            |

| UART0_TXDSerial port 0 send (receive)TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)6CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LDO OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | P2_7         |                                            |

| TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | CLKO         | Clock output (for debugging)               |

| TIM0_CH0Timer0 channel 0TIM3_CH1Timer3 channel 1ADC_TRIGGER1ADC1 trigger signal output (for debugging)CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | UART0_TXD    | Serial port 0 send (receive)               |

| ADC_TRIGGER1ADC1 trigger signal output (for debugging)6CLUOUT1CLU1 outputADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | Timer0 channel 0                           |

| 6       CLUOUT1       CLU1 output         ADC0_CH11       ADC0 Channel 11         OPAx_OUT       Op Amp Output         LD015       1.5V LD0 Output         REF       Reference Voltage         EXTI11       External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | TIM3_CH1     | Timer3 channel 1                           |

| ADC0_CH11ADC0 Channel 11OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | ADC_TRIGGER1 | ADC1 trigger signal output (for debugging) |

| OPAx_OUTOp Amp OutputLD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6 | CLUOUT1      | CLU1 output                                |

| LD0151.5V LD0 OutputREFReference VoltageEXTI11External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | ADC0_CH11    | ADC0 Channel 11                            |

| REF     Reference Voltage       EXTI11     External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | OPAx_OUT     | Op Amp Output                              |

| EXTI11 External GPIO Interrupt Signal 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | LDO15        | 1.5V LDO Output                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | REF          | Reference Voltage                          |

| WK6 External wake-up signal 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | EXTI11       | External GPIO Interrupt Signal 11          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | WK6          | External wake-up signal 6                  |

|    | PU           | Built-in $10k\Omega$ pull-up resistor, software can be turned off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | VDD          | Supply voltage of devices in the chip, 5V LDO output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |