© 2023 All rights reserved by Linko Semiconductor

Confidential. Unauthorized dissemination is prohibited.

# Catalog

| T | ABLE OF  | CONTENTS                          | اا |

|---|----------|-----------------------------------|----|

| P | ICTURE I | DIRECTORY                         |    |

| 1 | DOCU     | MENT CONVENTION                   | 1  |

|   | 1.1 R    | egister Read/Write Permissions    | 1  |

|   | 1.2      | LOSSARY OF ABBREVIATIONS          | 1  |

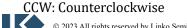

| 2 | OVER     | VIEW                              | 3  |

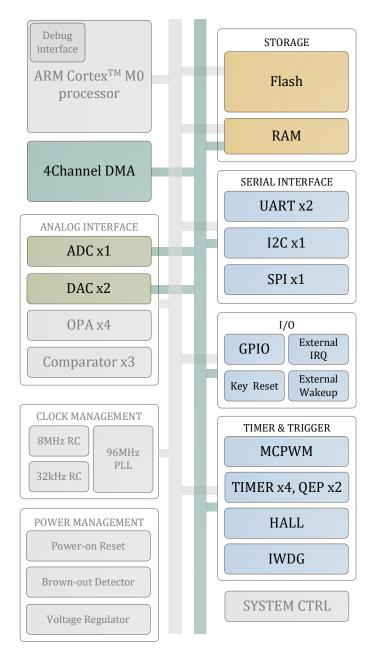

|   | 2.1 B    | RIEF DESCRIPTION                  | 3  |

|   | 2.2 C    | HARACTERISTIC                     | 3  |

|   | 2.2.1    | Memory                            | 3  |

|   | 2.2.2    | Clock                             | 3  |

|   | 2.2.3    | Peripheral module                 | 3  |

|   | 2.2.4    | Simulation module                 | 4  |

|   | 2.3 R    | ESOURCE DIAGRAM                   | 5  |

| 3 | ADDR     | ESS SPACE                         | 6  |

| 4 |          | RRUPT                             |    |

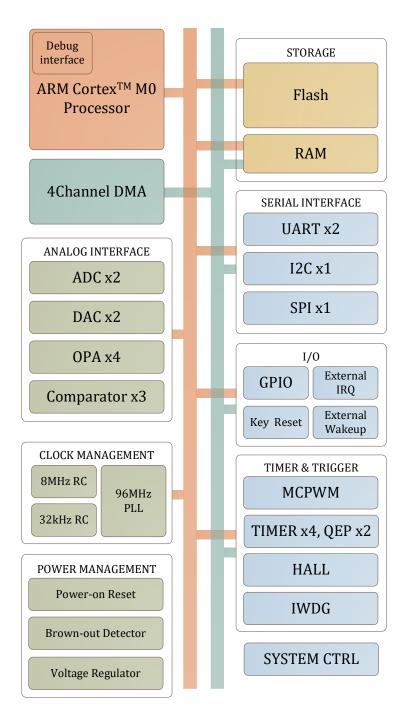

| 5 | ANAL     | OG CIRCUIT                        | 9  |

|   | 5.1 In   | ITRODUCTION                       | 9  |

|   | 5.1.1    | Power management system           | 10 |

|   | 5.1.2    | Clock system                      | 11 |

|   | 5.1.3    | Bandgap Voltage Reference (BGP)   | 11 |

|   | 5.1.4    | Analog-to-digital Converter (ADC) | 12 |

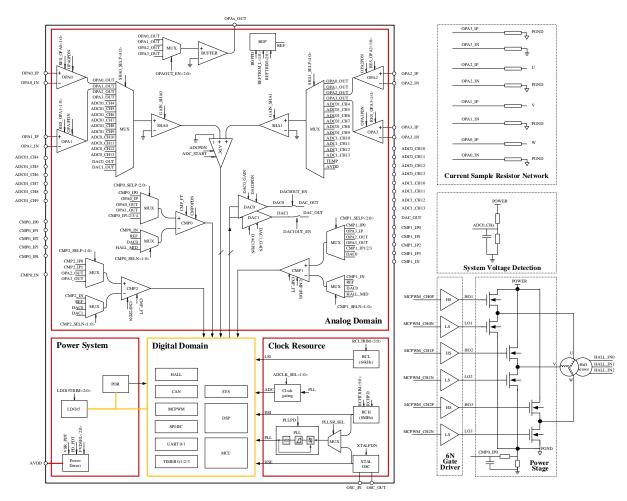

|   | 5.1.5    | Operational Amplifier (OPA)       | 12 |

|   | 5.1.6    | Comparator                        | 13 |

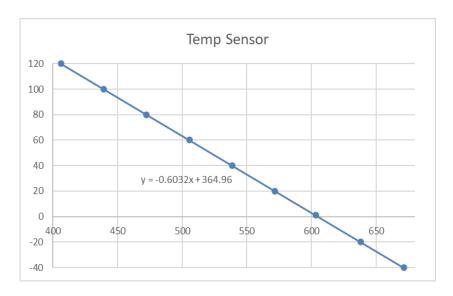

|   | 5.1.7    | Temperature sensor                | 14 |

|   | 5.1.8    | DAC module                        | 15 |

|   | 5.2 R    | EGISTER                           |    |

|   | 5.2.1    | Address assignment                |    |

|   | 5.2.2    | SYS_AFE_INFO                      |    |

|   |          | SYS_AFE_DBG                       |    |

|   | 5.2.5    | 0.000                             | 10 |

| 5.2.4                                                 | SYS_AFE_REGO                                                                                                                                                                                                                    | 18                                           |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 5.2.5                                                 | SYS_AFE_REG1                                                                                                                                                                                                                    | 19                                           |

| 5.2.6                                                 | SYS_AFE_REG2 Analog Configuration 2                                                                                                                                                                                             | 20                                           |

| 5.2.7                                                 | SYS_AFE_REG3 Analog Configuration Register 3                                                                                                                                                                                    | 21                                           |

| 5.2.8                                                 | SYS_AFE_REG4 Analog Configuration 4                                                                                                                                                                                             | 22                                           |

| 5.2.9                                                 | SYS_AFE_REG5 Analog Configuration 5                                                                                                                                                                                             | 23                                           |

| 5.2.10                                                | SYS_AFE_REG6 Analog Configuration 6                                                                                                                                                                                             | 24                                           |

| 5.2.11                                                | SYS_AFE_REG7 Analog Configuration Register 7                                                                                                                                                                                    | 25                                           |

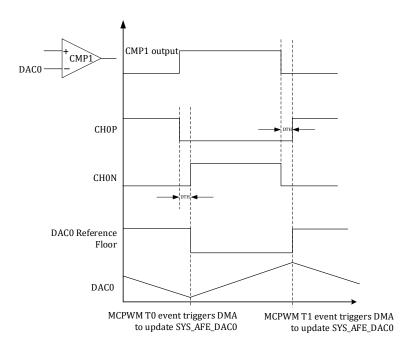

| 5.2.12                                                | SYS_AFE_DAC_CTRL DAC control register                                                                                                                                                                                           | 25                                           |

| 5.2.13                                                | SYS_AFE_DACO DACO Digital Register                                                                                                                                                                                              | 26                                           |

| 5.2.14                                                | SYS_AFE_DAC1 DAC1 digital register                                                                                                                                                                                              | 27                                           |

| 5.2.15                                                | SYS_AFE_DACO_AMC DACO Gain Correction Register                                                                                                                                                                                  | 27                                           |

| 5.2.16                                                | SYS_AFE_DACO_DC DACO DC offset register                                                                                                                                                                                         | 27                                           |

| 5.2.17                                                | SYS_AFE_DAC1_AMC DAC1 Gain Correction Register                                                                                                                                                                                  | 28                                           |

| 5.2.18                                                | SYS_AFE_DAC1_DC DAC1 DC offset register                                                                                                                                                                                         | 28                                           |

|                                                       |                                                                                                                                                                                                                                 |                                              |

| 6 SYST                                                | EM CONTROL AND CLOCK RESET                                                                                                                                                                                                      | 30                                           |

|                                                       |                                                                                                                                                                                                                                 |                                              |

|                                                       | EM CONTROL AND CLOCK RESET                                                                                                                                                                                                      | 30                                           |

| 6.1 (<br>6.1.1                                        | EM CONTROL AND CLOCK RESET                                                                                                                                                                                                      | 30<br>30                                     |

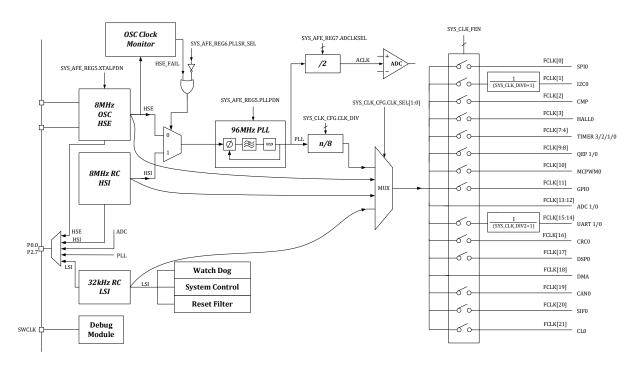

| 6.1 (<br>6.1.1                                        | EM CONTROL AND CLOCK RESET  Clock source                                                                                                                                                                                        | 30<br>30<br>32                               |

| 6.1 (<br>6.1.1<br>6.2 F                               | CLOCK                                                                                                                                                                                                                           | 30<br>30<br>32                               |

| 6.1 (6.1.1) 6.2 F 6.2.1                               | CLOCK                                                                                                                                                                                                                           | 30<br>32<br>32                               |

| 6.1 (6.1.1) 6.2 F 6.2.1                               | CLOCK                                                                                                                                                                                                                           | 30<br>32<br>32<br>32                         |

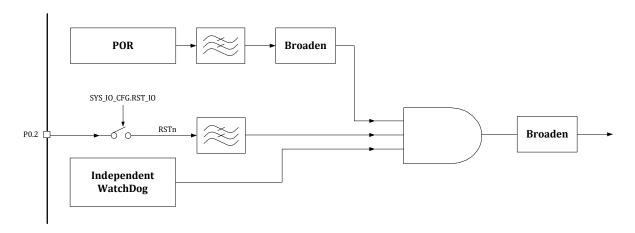

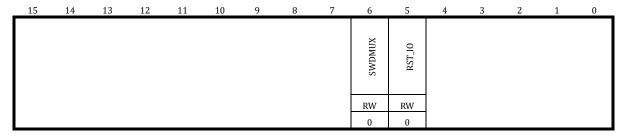

| 6.1 (6.1.1) 6.2 F 6.2.1                               | EM CONTROL AND CLOCK RESET  Clock source  Reset source  1.1 Hardware reset  5.2.1.1.1 Hardware reset architecture  5.2.1.1.2 Hardware reset logging                                                                             | 30<br>32<br>32<br>32<br>33                   |

| 6.1 (6.1.1) 6.2 F 6.2.1                               | EM CONTROL AND CLOCK RESET  Clock source  Reset source  1.1 Hardware reset  5.2.1.1.1 Hardware reset architecture  5.2.1.1.2 Hardware reset logging                                                                             | 303232323333                                 |

| 6.1 (6.1.1) 6.2 F 6.2.1 6.2.6 6.2.6 6.2.2             | EM CONTROL AND CLOCK RESET  Clock source  RESET  Reset source  1.1 Hardware reset  5.2.1.1.1 Hardware reset architecture  5.2.1.1.2 Hardware reset logging  1.2 Software reset                                                  | 30<br>32<br>32<br>33<br>33                   |

| 6.1 (6.1.1) 6.2 F 6.2.1 6.2.6 6.2.6 6.2.2             | EM CONTROL AND CLOCK RESET  Clock source  Reset source  1.1 Hardware reset  5.2.1.1.1 Hardware reset architecture  5.2.1.1.2 Hardware reset logging  1.2 Software reset  Resets the scope.                                      | 30<br>32<br>32<br>33<br>33<br>33             |

| 6.1 (6.1.1) 6.2 (6.2.1) 6.2.1 6.2.1 6.2.2 6.3 (6.2.2) | EM CONTROL AND CLOCK RESET  Clock source  Reset source  1.1 Hardware reset  5.2.1.1.1 Hardware reset architecture  5.2.1.1.2 Hardware reset logging  1.2 Software reset  Resets the scope                                       | 30<br>32<br>32<br>33<br>33<br>33<br>34<br>35 |

| 6.1 6.1.1 6.2 F 6.2.1 6.2.6 6.2.2 6.3 F 6.3.1         | EM CONTROL AND CLOCK RESET  Clock source  RESET  Reset source  1.1 Hardware reset  5.2.1.1.1 Hardware reset architecture  5.2.1.1.2 Hardware reset logging  1.2 Software reset  Resets the scope  REGISTER.  Address assignment | 30<br>32<br>32<br>33<br>33<br>33<br>35       |

3

| 6.3.5 SYS_CLK_DIV0 peripheral clock divide register 0                                                    | 38 |

|----------------------------------------------------------------------------------------------------------|----|

| 6.3.6 SYS_CLK_DIV2 Peripheral Clock Divide Register 2                                                    | 39 |

| 6.3.7 SYS_CLK_FEN Peripheral Clock Gating Register                                                       | 39 |

| 6.3.8 SYS_SFT_RST soft reset register                                                                    | 41 |

| 6.3.9 SYS_PROTECT Write Protect Register                                                                 | 43 |

| 6.3.10 SYS_FLSE Erase Protection Register                                                                | 44 |

| 6.3.11 SYS_FLSP Program Protection Register                                                              | 44 |

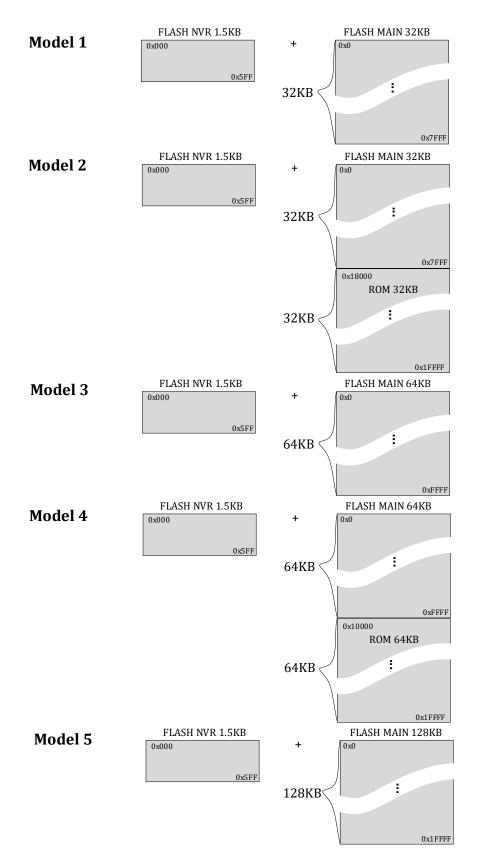

| 7 NON-VOLATILE MEMORY                                                                                    | 45 |

| 7.1 Introduction                                                                                         | 45 |

| 7.2 FUNCTIONAL FEATURES                                                                                  | 47 |

| 7.2.1 Functional description                                                                             | 47 |

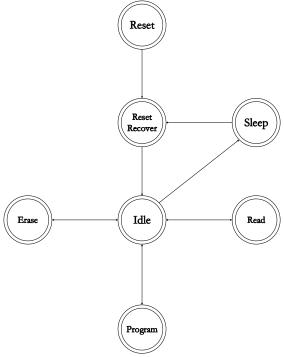

| 7.2.1.1 Reset operation                                                                                  | 48 |

| 7.2.1.2 Sleep operation                                                                                  | 48 |

| 7.2.1.3 Read operation                                                                                   | 48 |

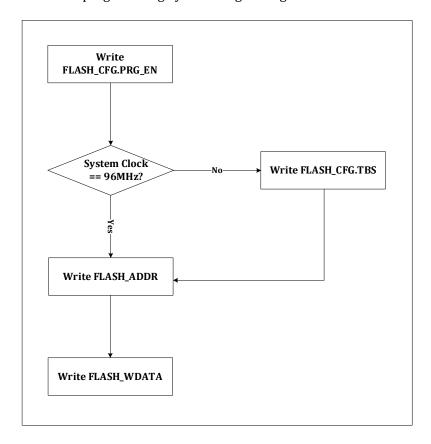

| 7.2.1.4 FLASH programming operation                                                                      | 49 |

| 7.2.1.5 FLASH erase operation                                                                            | 51 |

| 7.2.1.6 FLASH prefetch operation                                                                         | 52 |

| 7.2.1.7 Non-volatile memory bank protection                                                              | 52 |

| 7.2.1.8 FLASH Online Upgrade (IAP)                                                                       | 54 |

| 7.2.1.8.1 Turn on interrupted online upgrade                                                             | 54 |

| 7.2.1.8.2 Turn Off an Interrupted Online Upgrade                                                         | 55 |

| 7.2.1.8.3 Location of Online Upgrade Function                                                            | 55 |

| 7.3 REGISTER                                                                                             | 55 |

| 7.3.1 Address assignment                                                                                 | 55 |

| 7.3.2 FLASH_CFG configuration register (recommended to read back first and modify by or/and)             | 56 |

| 7.3.3 FLASH_ADDR Address Register                                                                        | 57 |

| 7.3.4 FLASH_WDATA Write Data Register                                                                    | 57 |

| 7.3.5 FLASH_RDATA Read Data Register                                                                     | 58 |

| 7.3.6 FLASH_ERASE Erase Control Register                                                                 | 58 |

| 7.3.7 FLASH_PROTECT Protection Status Register                                                           | 58 |

| ©2023 All rights reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. |    |

| 7   | 3.8                                         | FLAS                                                                                        | SH_READY                                                                               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 3.9                                         | FLAS                                                                                        | SH_SIZE capacity register                                                              | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | 3.10                                        | FL                                                                                          | LASH_NCFG configuration register (recommended to read back first and modify by or/and) | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | 3.11                                        | FL                                                                                          | LASH_NADDR Address Register                                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | 3.12                                        | FL                                                                                          | LASH_NWDATA Write Data Register                                                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | 3.13                                        | FL                                                                                          | LASH_NRDATA Read Data Register                                                         | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | 3.14                                        | FL                                                                                          | LASH_NERASE Erase Control Register                                                     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

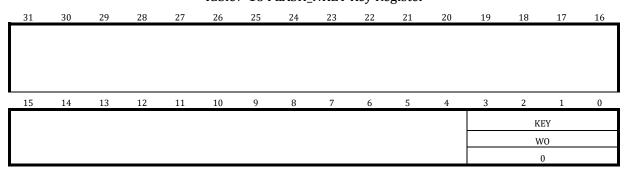

| 7.  | 3.15                                        | FL                                                                                          | LASH_NKEY Key Register                                                                 | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SF  | PI                                          |                                                                                             |                                                                                        | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.1 | O,                                          | VERVIE                                                                                      | EW                                                                                     | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.2 | M                                           | lain ci                                                                                     | HARACTERISTICS                                                                         | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

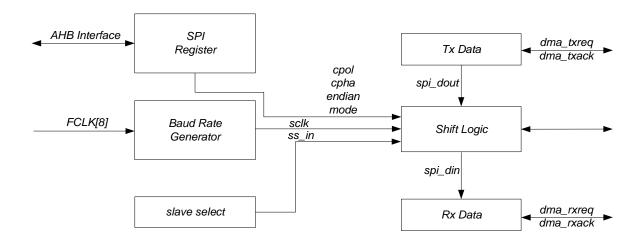

| 8.3 | Fu                                          | JNCTIC                                                                                      | ONAL DESCRIPTION                                                                       | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

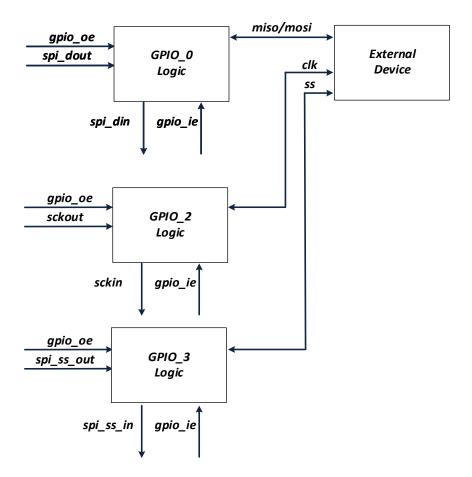

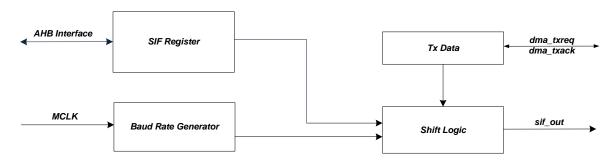

| 8.3 | 3.1                                         | Fund                                                                                        | ctional block diagram                                                                  | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.3 | 3.2                                         | Fund                                                                                        | ctional description                                                                    | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 8.3.2                                       | .1                                                                                          | Full duplex mode                                                                       | .68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

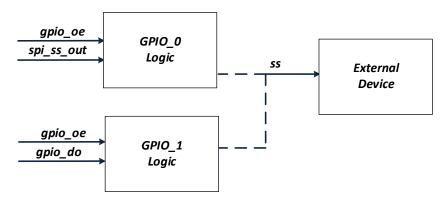

|     | 8.3.2                                       | 2                                                                                           | Half-duplex mode                                                                       | .69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

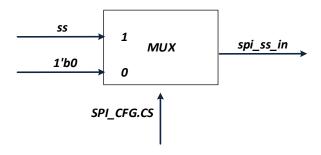

|     | 8.3.2                                       | 3                                                                                           | Chip select signal                                                                     | .71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 8.3.2                                       | .4                                                                                          | Communication format                                                                   | .71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 8.3.2                                       | 5                                                                                           | Data format and length                                                                 | .71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 8.3.2                                       | 6                                                                                           | DMA transfer                                                                           | .72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 8.3.2                                       | .7                                                                                          | MCU transmission                                                                       | .72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 8.3.2                                       | 8                                                                                           | External event transmission                                                            | .73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

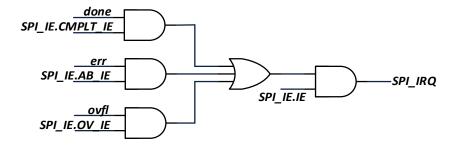

|     | 8.3.2                                       | .1                                                                                          | Interrupt Handling                                                                     | .73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 8.3.2                                       | 2                                                                                           | Baud rate setting                                                                      | .74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.4 | Re                                          | GISTE                                                                                       | ir                                                                                     | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.4 | 4.1                                         | Add                                                                                         | ress assignment                                                                        | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.4 | 4.2                                         | SPI_                                                                                        | CFG SPI control register                                                               | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.4 | 4.3                                         | SPI_                                                                                        | IE SPI Interrupt Register                                                              | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.4 | 4.4                                         | SPI_                                                                                        | BAUD SPI Baud Rate Register                                                            | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8.4 | 4.5                                         | SPI_                                                                                        | TXDATA SPI data transmit register                                                      | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 7 7 7 7 7 8.1 8.2 8.3 8 8.4 8.4 8.4 8.6 8.6 | 8.1 O' 8.2 M 8.3 Ft 8.3.1 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 8.3.2 | 7.3.9 FLA. 7.3.10 F. 7.3.11 F. 7.3.12 F. 7.3.13 F. 7.3.14 F. 7.3.15 F. SPI             | 7.3.9 FLASH_NCFG configuration register (recommended to read back first and modify by or/and). 7.3.11 FLASH_NADDR Address Register. 7.3.12 FLASH_NWDATA Write Data Register. 7.3.13 FLASH_NRDATA Read Data Register. 7.3.14 FLASH_NREASE Erase Control Register. 7.3.15 FLASH_NKEY Key Register. 8.1 OVERVIEW. 8.2 MAIN CHARACTERISTICS. 8.3 FUNCTIONAL DESCRIPTION. 8.3.1 Functional block diagram. 8.3.2 Functional description. 8.3.2.1 Full duplex mode. 8.3.2.2 Half-duplex mode. 8.3.2.3 Chip select signal. 8.3.2.4 Communication format. 8.3.2.5 Data format and length. 8.3.2.6 DMA transfer. 8.3.2.7 MCU transmission. 8.3.2.8 External event transmission. 8.3.2.1 Interrupt Handling. 8.3.2.2 Baud rate setting. 8.4 REGISTER. 8.4.1 Address assignment. 8.4.2 SPI_CFG SPI control register. 8.4.3 SPI_IE SPI Interrupt Register. |

| 8.4.6 SPI_RXDATA SPI data receive register       | 77 |

|--------------------------------------------------|----|

| 8.4.7 SPI_SIZE SPI Data Transfer Length Register | 77 |

| 9 12C                                            | 79 |

| 9.1 Overview                                     | 79 |

| 9.2 Main Characteristics                         | 79 |

| 9.3 FUNCTIONAL DESCRIPTION                       | 79 |

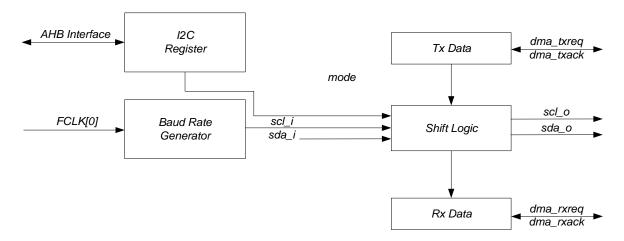

| 9.3.1 Functional block diagram                   | 79 |

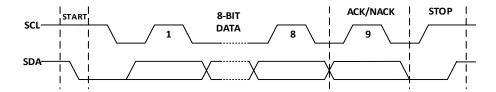

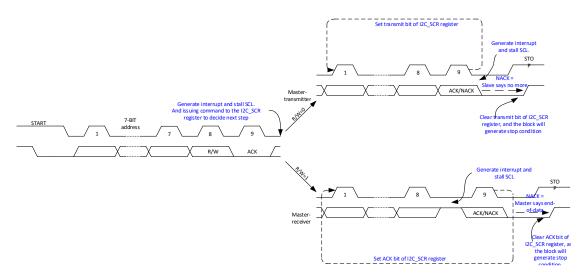

| 9.3.2 Functional description                     | 80 |

| 9.3.2.1 Mode selection                           | 80 |

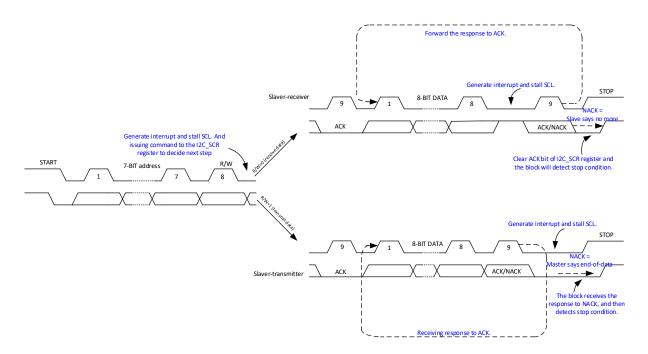

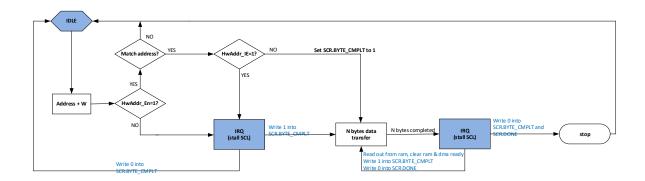

| 9.3.2.2 Slave mode                               | 82 |

| 9.3.2.2.1 Slave Mode Transmission                | 82 |

| 9.3.2.2.2 Slave Mode Transport                   | 83 |

| 9.3.2.2.3 Receive from Mode Single Byte          | 83 |

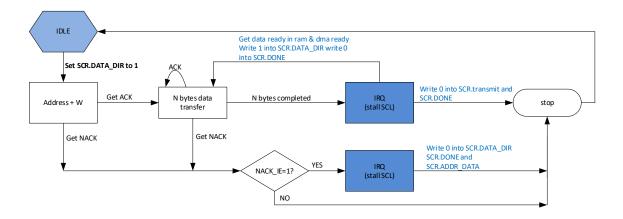

| 9.3.2.3 Slave Mode DMA Transfer                  | 84 |

| 9.3.2.3.1 Slave Mode DMA Transmit                | 84 |

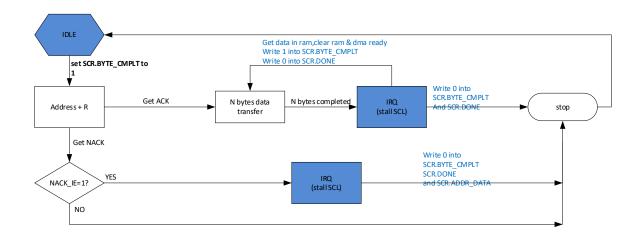

| 9.3.2.3.2 Slave Mode DMA Receive                 | 85 |

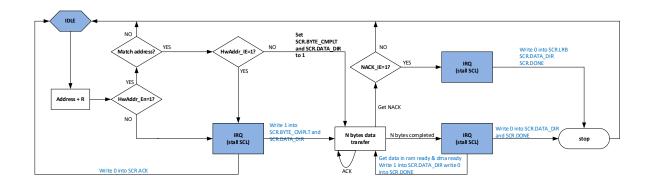

| 9.3.2.4 Master mode                              | 85 |

| 9.3.2.4.1 Main mode single byte transfer         | 86 |

| 9.3.2.4.2 Master Mode Single Byte Send           | 86 |

| 9.3.2.4.3 Master Mode Single Byte Receive        | 87 |

| 9.3.2.4.4 Master mode DMA transfer               | 87 |

| 9.3.2.4.5 Master Mode DMA Transmit               | 87 |

| 9.3.2.4.6 Master mode DMA receive                | 88 |

| 9.3.2.5 DMA transfer                             | 89 |

| 9.3.2.6 I2C bus exception handling               | 90 |

| 9.3.2.7 Interrupt Handling                       | 90 |

| 9.3.2.8 Communication speed setting              | 91 |

| 9.4 Register                                     | 91 |

| 9.4.1 Address assignment                         | 91 |

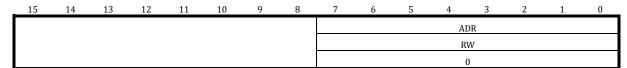

| 9.4.2 I2C_ADDR Address Register                  | 91 |

| 9.4.3 | 3 I2C_CFG system control register                                                                        | 92  |

|-------|----------------------------------------------------------------------------------------------------------|-----|

| 9.4.4 | 4 I2C_SCR status control register                                                                        | 93  |

| 9.4.5 | 5 I2C_DATA Data Register                                                                                 | 94  |

| 9.4.6 | 6 I2C_MSCR Master Mode Register                                                                          | 94  |

| 9.4.7 | 7 I2C_BCR I2C transfer control register                                                                  | 95  |

| 9.4.8 | B I2C_B SIZE I2C Transfer Length Register                                                                |     |

| 10 CI | MP                                                                                                       | 96  |

| 10.1  | Overview                                                                                                 | 96  |

| 10.2  | REGISTER                                                                                                 | 96  |

| 10.2. | .1 Address assignment                                                                                    | 96  |

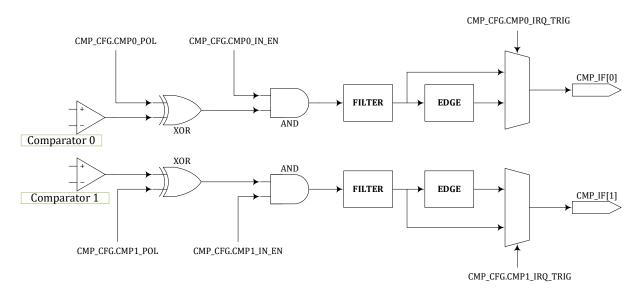

| 10.2. | .2 CMP_IE Interrupt enable register                                                                      | 96  |

| 10.2. | .3 CMP_IF Interrupt Flag Register                                                                        | 97  |

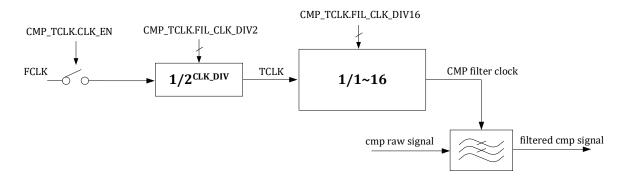

| 10.2. | .4 CMP_TCLK Divided clock control register                                                               | 97  |

| 10.2. | .5 CMP_CFG Control Register                                                                              | 99  |

| 10.2. | .6 CMP_BLCWIN Windowing control register                                                                 | 102 |

| 10.2. | .7 CMP_DATA Output Data Register                                                                         | 103 |

| 11 H. | ALL                                                                                                      | 104 |

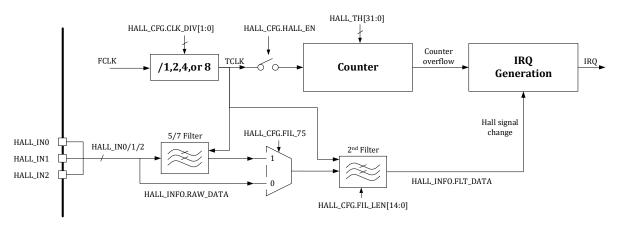

| 11.1  | Overview                                                                                                 | 104 |

| 11.2  | IMPLEMENTATION DESCRIPTION                                                                               | 104 |

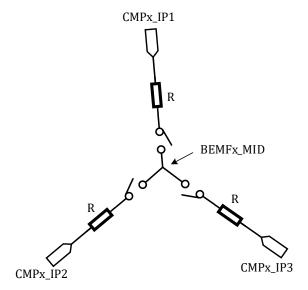

| 11.2. | .1 Signal source                                                                                         | 104 |

| 11.2. | .2 Working clock                                                                                         | 104 |

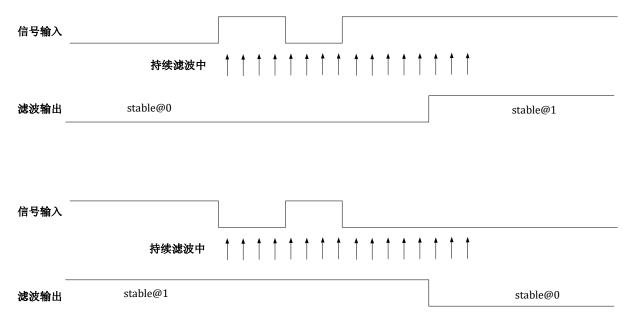

| 11.2. | .3 Signal filtering                                                                                      | 104 |

| 11.2. | .4 Capture                                                                                               | 105 |

| 11.2. | .5 Interrupt                                                                                             | 106 |

| 11.2. | .6 Data flow                                                                                             | 106 |

| 11.3  | REGISTER                                                                                                 | 106 |

| 11.3. | .1 Address assignment                                                                                    | 106 |

| 11.3. | .2 HALL_CFG HALL module configuration register                                                           | 106 |

| 11.3. | .3 HALL_INFO HALL module information register                                                            | 108 |

| 11.3. | .4 HALL_WIDTH HALL Width Meter Value Register                                                            | 108 |

|       | ©2023 All rights reserved by Linko Semiconductor Confidential. Unauthorized dissemination is prohibited. | 7   |

|    | 11.3.5   | HALL_TH HALL module counter threshold register | 109 |

|----|----------|------------------------------------------------|-----|

|    | 11.3.6   | HALL_CNT HALL count register                   | 109 |

| 12 | ADC      |                                                | 110 |

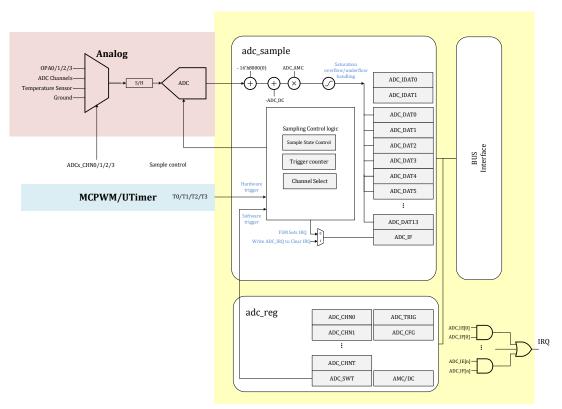

| 1  | 2.1 OVE  | RVIEW                                          | 110 |

|    | 12.1.1   | Functional block diagram                       | 110 |

|    | 12.1.2   | ADC trigger mode                               | 112 |

|    | 12.1.3   | ADC Channel Select                             | 112 |

|    | 12.1.4   | ADC Interrupt                                  | 113 |

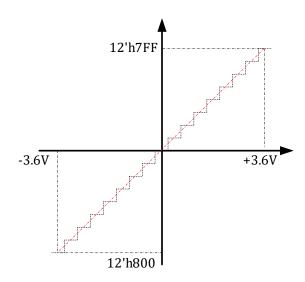

|    | 12.1.5   | ADC output number system                       | 113 |

|    | 12.1.6   | ADC range                                      | 114 |

|    | 12.1.7   | ADC correction                                 | 114 |

|    | 12.1.8   | ADC Threshold Monitoring (Analog Watchdog)     | 115 |

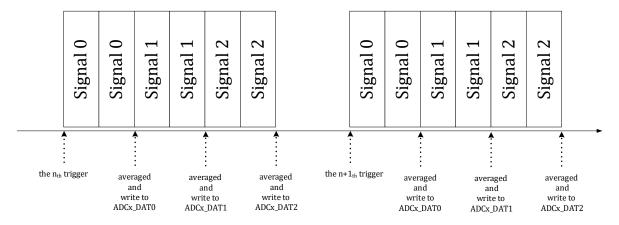

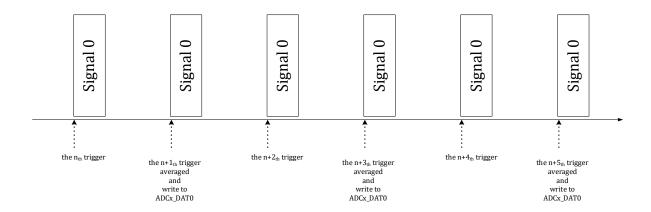

|    | 12.1.9   | Oversampling                                   | 116 |

| 1  | 2.2 REGI | ISTER                                          | 117 |

|    | 12.2.1   | Address assignment                             | 117 |

|    | 12.2.2   | Sample Data Register                           | 118 |

|    | 12.2.2.  | 1 ADCx_DAT0(x = 0,1)                           | 118 |

|    | 12.2.2.  | 2 ADCx_DAT1(x = 0,1)                           | 118 |

|    | 12.2.2.  | 3 ADCx_DAT2(x = 0,1)                           | 119 |

|    | 12.2.2.  | 4 ADCx_DAT3(x = 0,1)                           | 119 |

|    | 12.2.2.  | 5 ADCx_DAT4(x = 0,1)                           | 119 |

|    | 12.2.2.  | 6 ADCx_DAT5(x = 0,1)                           | 120 |

|    | 12.2.2.  | 7 ADCx_DAT6(x = 0,1)                           | 120 |

|    | 12.2.2.  | 8 ADCx_DAT7(x = 0,1)                           | 120 |

|    | 12.2.2.  | 9 ADCx_DAT8(x = 0,1)                           | 121 |

|    | 12.2.2.  | 10 ADCx_DAT9(x = 0,1)                          | 121 |

|    | 12.2.2.  | 11 ADCx_DAT10(x = 0,1)                         | 122 |

|    | 12.2.2.  | 12 ADCx_DAT11(x = 0,1)                         | 122 |

|    | 12.2.2.  | 13 ADCx_DAT12(x = 0,1)                         | 122 |

|    | 12.2.2.  | 14 ADCx_DAT13(x = 0,1)                         | 123 |

| 12.2.2.15 ADCx_IDAT0(x = 0,1)               | 123 |

|---------------------------------------------|-----|

| 12.2.2.16 ADCx_IDAT1(x = 0,1)               | 123 |

| 12.2.3 Signal source register               | 124 |

| 12.2.3.1 ADCx_CHN0(x = 0,1)                 | 124 |

| 12.2.3.2 ADCx_CHN1(x = 0,1)                 | 124 |

| 12.2.3.3 ADCx_CHN2(x = 0,1)                 | 124 |

| 12.2.3.4 ADCx_CHN3(x = 0,1)                 | 125 |

| 12.2.3.5 ADCx_ICHN(x = 0,1)                 | 125 |

| 12.2.3.6 ADC channel signal selection       | 126 |

| 12.2.4 Number of sampling channels register | 127 |

| 12.2.4.1 ADCx_CHNT(x = 0,1)                 | 127 |

| 12.2.5 Configuration register               | 127 |

| 12.2.5.1 ADCx_GAIN(x = 0,1)                 | 127 |

| 12.2.5.2 ADCx_CFG (x = 0,1)                 | 128 |

| 12.2.5.3 ADC0_TRIG                          | 129 |

| 12.2.5.4 ADC1_TRIG                          | 130 |

| 12.2.6 Software trigger register            | 131 |

| 12.2.6.1 ADCx_SWT(x = 0,1)                  | 131 |

| 12.2.7 Calibration register                 | 132 |

| 12.2.7.1 ADCx_DC0(x = 0,1)                  | 132 |

| 12.2.7.2 ADCx_AMC0(x = 0,1)                 | 133 |

| 12.2.7.3 ADCx_DC1(x = 0,1)                  | 133 |

| 12.2.7.4 ADCx_AMC1(x = 0,1)                 | 134 |

| 12.2.8 Interrupt register                   | 134 |

| 12.2.8.1 ADCx_IE(x = 0,1)                   | 134 |

| 12.2.8.2 ADCx_IF(x = 0,1)                   | 135 |

| 12.2.9 Analog watchdog                      | 136 |

| 12.2.9.1 ADC0_LTH                           | 136 |

| 12.2.9.2 ADC0_HTH                           | 136 |

| 12.2.9.3 ADC0_GEN                           | 136 |

| 12.3 APPLICATION GUIDE                                        | 137 |

|---------------------------------------------------------------|-----|

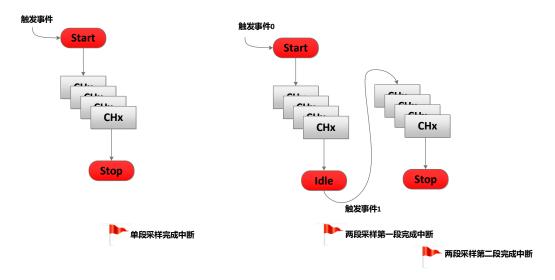

| 12.3.1 ADC Sampling Trigger Mode                              | 137 |

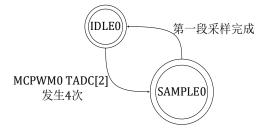

| 12.3.1.1 Single-segment trigger mode                          | 138 |

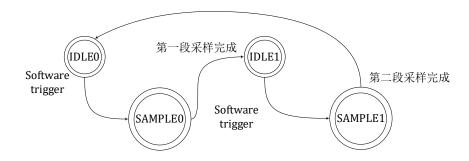

| 12.3.1.2 Two-stage trigger mode                               | 139 |

| 12.3.2 Interrupt                                              | 141 |

| 12.3.2.1 Single Segment Triggered Sampling Complete Interrupt | 141 |

| 12.3.2.2 Two-segment triggered sample complete interrupt      | 141 |

| 12.3.3 Configuration modification                             | 141 |

| 12.3.4 Select the corresponding analog channel                | 142 |

| 13 TIMER GENERAL TIMER                                        | 143 |

| 13.1 Overview                                                 | 143 |

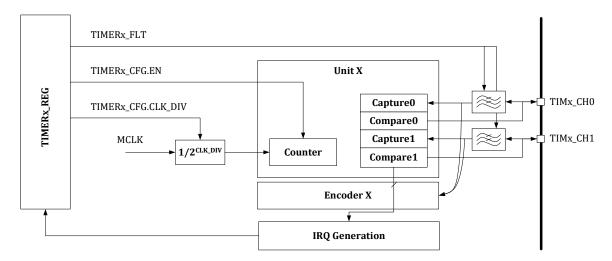

| 13.1.1 Functional block diagram                               | 143 |

| 13.1.1.1 Register module                                      | 143 |

| 13.1.1.2 IO filter module                                     | 143 |

| 13.1.1.3 General Timer Module                                 | 143 |

| 13.1.1.4 Clock divider module                                 | 144 |

| 13.1.2 Functional features                                    | 144 |

| 13.2 CHARACTERISTIC                                           | 144 |

| 13.2.1 Clock Division                                         | 144 |

| 13.2.2 The interrupt flag is cleared                          | 144 |

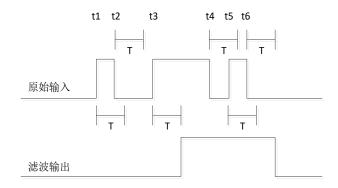

| 13.2.3 Filtering                                              | 144 |

| 13.2.4 Mode                                                   | 145 |

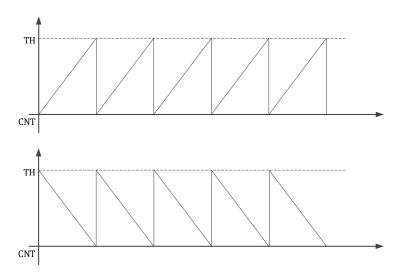

| 13.2.4.1 Counter                                              | 145 |

| 13.2.4.2 Capture mode                                         | 145 |

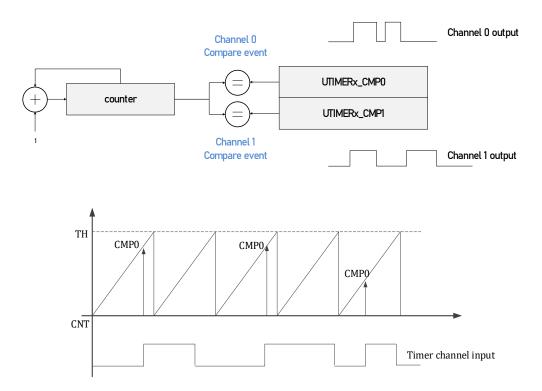

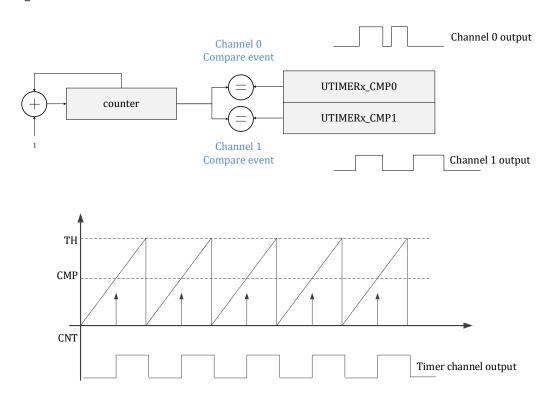

| 13.2.4.3 Compare mode (edge-aligned PWM)                      | 147 |

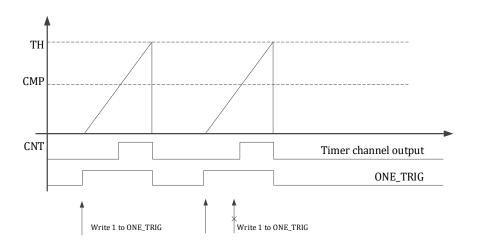

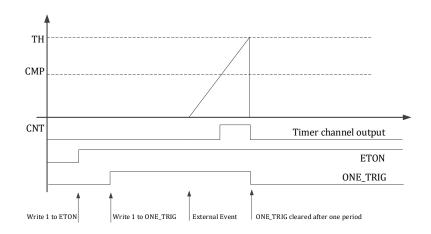

| 13.2.4.4 Single trigger                                       | 147 |

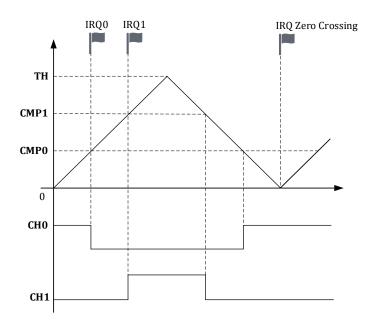

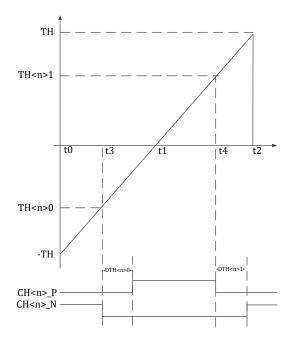

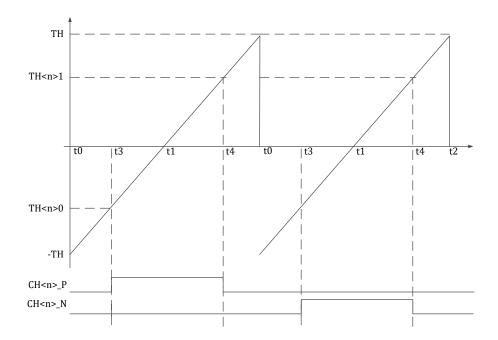

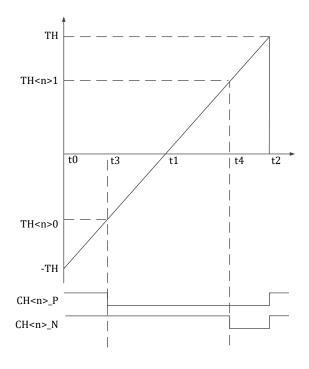

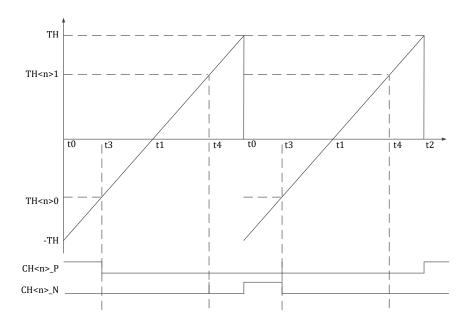

| 13.2.4.5 Center Mode (Complementary PWM)                      | 148 |

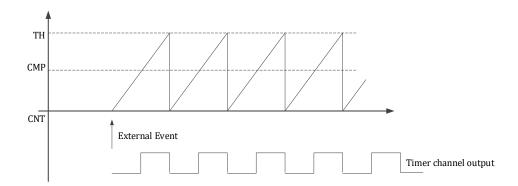

| 13.2.5 External events                                        | 149 |

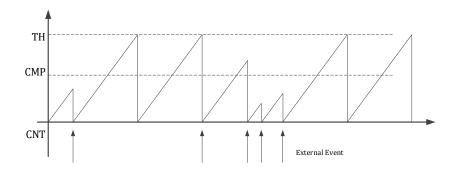

| 13.2.5.1.1 External start signal                              | 149 |

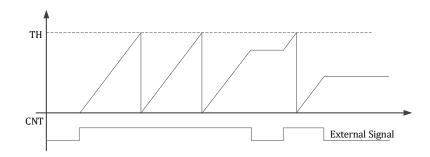

| 13.2.5.1.2 External clock signal                              | 150 |

| 13     | 3.2.5.2 | 3 External reset signal                               | 151 |

|--------|---------|-------------------------------------------------------|-----|

| 13     | 3.2.5.2 | 4 External gate signal                                | 151 |

| 13.2.6 | Α       | DC trigger                                            | 152 |

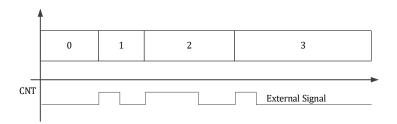

| 13.2.7 | E       | ncoder                                                | 152 |

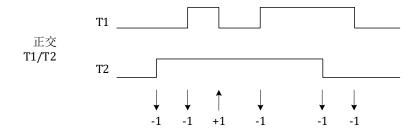

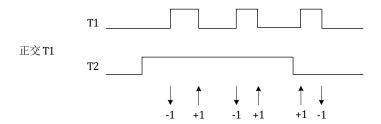

| 13.2   | .7.1    | Quadrature coded signal                               | 152 |

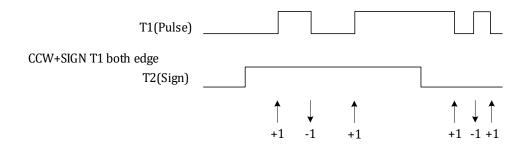

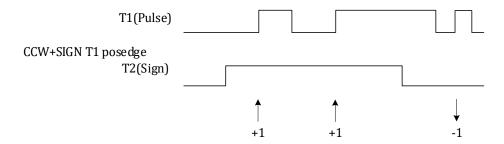

| 13.2   | .7.2    | Sign plus pulse signal                                | 153 |

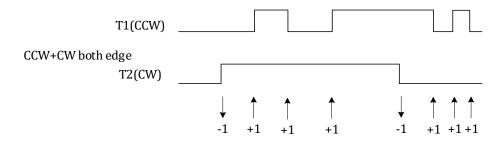

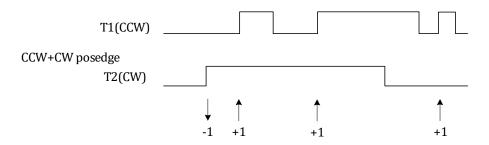

| 13.2   | .7.3    | CCW/CW double pulse signal                            | 154 |

| 13.3 R | EGISTE  | R                                                     | 155 |

| 13.3.1 | Α       | ddress assignment                                     | 155 |

| 13.3.2 | T       | MERO register                                         | 157 |

| 13.3   | .2.1    | TIMERO_CFG Timer0 configuration register              | 157 |

| 13.3   | .2.2    | TIMERO_TH Timer0 threshold register                   | 160 |

| 13.3   | .2.3    | TIMERO_CNT Timer0 count register                      | 160 |

| 13.3   | .2.4    | TIMERO_CMP0 Timer0 Channel 0 Compare Capture Register | 161 |

| 13.3   | .2.5    | TIMERO_CMP1 Timer0 Channel 1 Compare Capture Register | 161 |

| 13.3   | .2.6    | TIMERO_EVT Timer0 external event select register      | 162 |

| 13.3   | .2.7    | TIMER0_FLT Timer0 filter control register             | 164 |

| 13.3   | .2.8    | TIMERO_IE Timer0 Interrupt Enable Register            | 164 |

| 13.3   | .2.9    | TIMERO_IF Timer0 Interrupt Flag register              | 165 |

| 13.3   | .2.10   | TIMERO_IO Timer0 IO control register                  | 166 |

| 13.3.3 | T       | MER1 register                                         | 167 |

| 13.3   | .3.1    | TIMER1_CFG Timer1 configuration register              | 167 |

| 13.3   | .3.2    | TIMER1_TH Timer 1 threshold register                  | 169 |

| 13.3   | .3.3    | TIMER1_CNT Timer1 count register                      | 170 |

| 13.3   | .3.4    | TIMER1_CMP0 Timer1 Channel 0 Compare Capture Register | 170 |

| 13.3   | .3.5    | TIMER1_CMP1 Timer1 Channel 1 Compare Capture Register | 171 |

| 13.3   | .3.6    | TIMER1_EVT Timer1 external event select register      | 171 |

| 13.3   | .3.7    | TIMER1_FLT Timer1 filter control register             | 173 |

| 13.3   | .3.8    | TIMER1_IE Timer1 Interrupt Enable Register            | 174 |

| 13.3   | .3.9    | TIMER1_IF Timer1 Interrupt Flag register              | 174 |

| 13.3.4   | TIMER2 register                                       | 175 |

|----------|-------------------------------------------------------|-----|

| 13.3.4.1 | TIMER2_CFG Timer2 configuration register              | 175 |

| 13.3.4.2 | TIMER2_TH Timer2 threshold register                   | 178 |

| 13.3.4.3 | TIMER2_CNT Timer2 count register                      | 178 |

| 13.3.4.4 | TIMER2_CMP0 Timer2 Channel 0 Compare Capture Register | 179 |

| 13.3.4.5 | TIMER2_CMP1 Timer2 Channel 1 Compare Capture Register | 179 |

| 13.3.4.6 | TIMER2_EVT Timer2 external event select register      | 180 |

| 13.3.4.7 | TIMER2_FLT Timer2 filter control register             | 182 |

| 13.3.4.8 | TIMER2_IE Timer2 Interrupt Enable Register            | 182 |

| 13.3.4.9 | TIMER2_IF Timer2 Interrupt Flag register              | 183 |

| 13.3.5   | TIMER3 register                                       | 184 |

| 13.3.5.1 | TIMER3_CFG Timer3 configuration register              | 184 |

| 13.3.5.2 | TIMER3_TH Timer3 threshold register                   | 187 |

| 13.3.5.3 | TIMER3_CNT Timer3 count register                      | 187 |

| 13.3.5.4 | TIMER3_CMP0 Timer3 Channel 0 Compare Capture Register | 188 |

| 13.3.5.5 | TIMER3_CMP1 Timer3 Channel 1 Compare Capture Register | 188 |

| 13.3.5.6 | TIMER3_EVT Timer3 external event select register      | 188 |

| 13.3.5.7 | TIMER3_FLT Timer3 filter control register             | 190 |

| 13.3.5.8 | TIMER3_IE Timer3 Interrupt Enable Register            | 191 |

| 13.3.5.9 | TIMER3_IF Timer3 Interrupt Flag register              | 192 |

| 13.3.6   | QEPO register                                         | 193 |

| 13.3.6.1 | QEP0_CFG QEP0 Configuration Register                  | 193 |

| 13.3.6.2 | QEP0_TH QEP0 Count Threshold Register                 | 194 |

| 13.3.6.3 | QEP0_CNT QEP0 count register                          | 194 |

| 13.3.6.4 | QEP0_IE QEP0 Interrupt Enable Register                | 194 |

| 13.3.6.5 | QEP0_IF QEP0 Interrupt Flag register                  | 195 |

| 13.3.7   | QEP1 register                                         | 195 |

| 13.3.7.1 | QEP1_CFG QEP1 Configuration Register                  | 195 |

| 13.3.7.2 | QEP 1_TH QEP1 Count Threshold Register                | 196 |

| 13.3.7.3 | QEP1_CNT QEP1 Count Register                          | 197 |

|    | 13.3.7.4                                                                 | 4 QEP1_IE QEP1 Interrupt Enable Register                                                       | 197                             |

|----|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|

|    | 13.3.7.5                                                                 | QEP1_IF QEP1 Interrupt Flag register                                                           | 197                             |

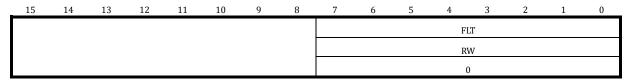

| 14 | MCPW                                                                     | /M                                                                                             | 199                             |

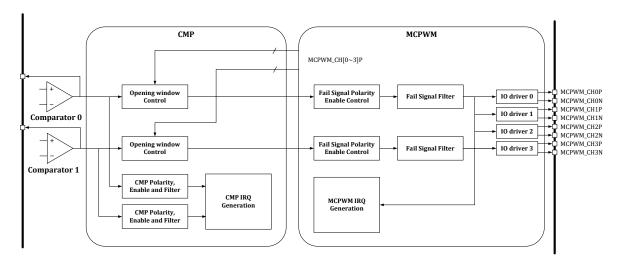

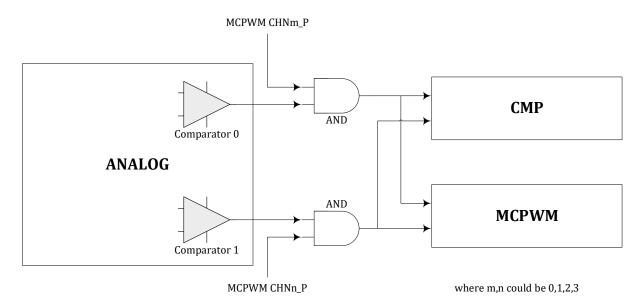

| 1  | 4.1 OVE                                                                  | RVIEW                                                                                          | 199                             |

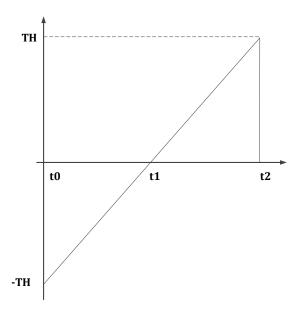

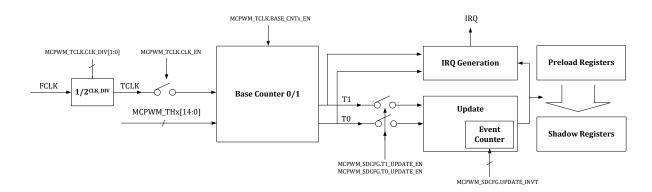

|    | 14.1.1                                                                   | Base Counter module                                                                            | 200                             |

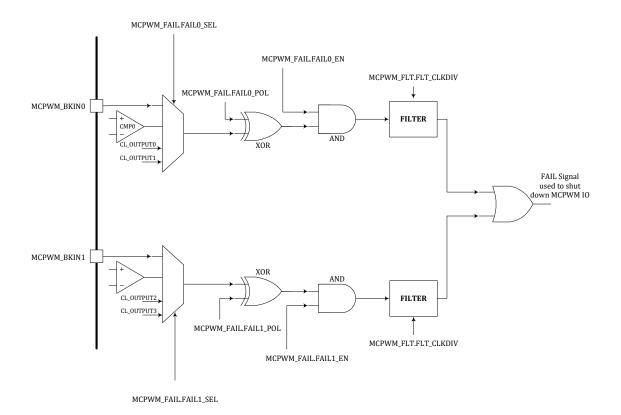

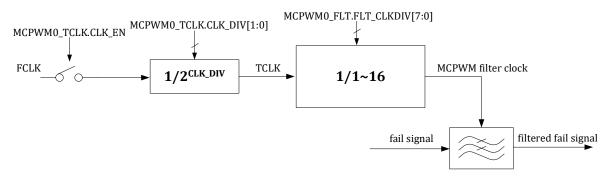

|    | 14.1.2                                                                   | FAIL signal processing                                                                         | 202                             |

|    | 14.1.3                                                                   | MCPWM Special Output Status                                                                    | 204                             |

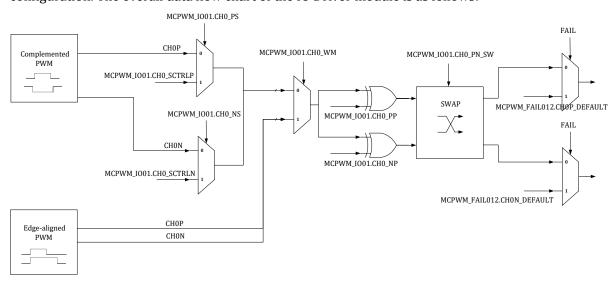

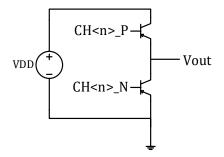

|    | 14.1.4                                                                   | IO DRIVER module                                                                               | 204                             |

|    | 14.1.4.1                                                                 | MCPWM Wave-form Output: Center-aligned Mode                                                    | 204                             |

|    | 14.1.4.2                                                                 | MCPWM Wave-form Control: Center-aligned Push-pull Mode                                         | 205                             |

|    | 14.1.4.3                                                                 | MCPWM Wave-form Output: Edge-aligned Mode                                                      | 206                             |

|    | 14.1.4.4                                                                 | MCPWM Waveform Control-Edge Aligned Push-Pull Mode                                             | 207                             |

|    | 14.1.4.5                                                                 | MCPWM IO : Dead-zone Control                                                                   | 207                             |

|    | 14.1.4.6                                                                 | 6 MCPWM IO: Polarity Settings                                                                  | 208                             |

|    | 14.1.4.7                                                                 | 7 MCPWM IO: Auto- Protection                                                                   | 208                             |

|    | 14.1.5                                                                   | ADC Trigger Timer module                                                                       | 208                             |

|    | 1116                                                                     | Digital navor applications                                                                     | 200                             |

|    | 14.1.6                                                                   | Digital power applications                                                                     | 209                             |

|    | 14.1.7                                                                   | Interrupt                                                                                      |                                 |

| 1  | 14.1.7                                                                   |                                                                                                | 211                             |

| 1  | 14.1.7                                                                   | Interrupt                                                                                      | 211<br>212                      |

| 1  | <i>14.1.7</i><br>4.2 Regi:                                               | Interrupt                                                                                      | 211<br>212<br>212               |

| 1  | 14.1.7<br>4.2 REGI:<br>14.2.1                                            | Interrupt  STER  Address assignment                                                            | 211<br>212<br>212<br>214        |

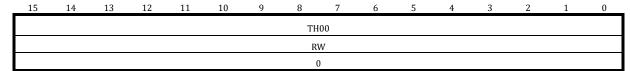

| 1  | 14.1.7<br>4.2 REGIS<br>14.2.1<br>14.2.2                                  | Interrupt  Address assignment  MCPWM0_TH00                                                     | 211<br>212<br>212<br>214<br>215 |

| 1  | 14.1.7<br>4.2 REGIS<br>14.2.1<br>14.2.2<br>14.2.3                        | Interrupt  Address assignment  MCPWM0_TH00  MCPWM0_TH01                                        | 211<br>212<br>212<br>214<br>215 |

| 1  | 14.1.7<br>4.2 REGIS<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4              | Interrupt  Address assignment  MCPWM0_TH00  MCPWM0_TH01  MCPWM0_TH10                           | 211212212214215215              |

| 1  | 14.1.7 4.2 REGIS 14.2.1 14.2.2 14.2.3 14.2.4 14.2.5                      | Interrupt  Address assignment  MCPWM0_TH00  MCPWM0_TH01  MCPWM0_TH10  MCPWM0_TH11              | 211212212214215215215           |

| 1  | 14.1.7 4.2 REGIS 14.2.1 14.2.2 14.2.3 14.2.4 14.2.5 14.2.6               | Interrupt  Address assignment  MCPWM0_TH00  MCPWM0_TH01  MCPWM0_TH11  MCPWM0_TH11  MCPWM0_TH20 | 211212212214215215215216216     |

| 1  | 14.1.7 4.2 REGIS 14.2.1 14.2.2 14.2.3 14.2.4 14.2.5 14.2.6 14.2.7        | Interrupt  Address assignment                                                                  | 211212214215215216216217        |

| 1  | 14.1.7 4.2 REGIS 14.2.1 14.2.2 14.2.3 14.2.4 14.2.5 14.2.6 14.2.7 14.2.8 | Interrupt                                                                                      | 211212214215215216216217217     |

| 14.2.12 | MCPWM0_TH50   | 218 |

|---------|---------------|-----|

| 14.2.13 | MCPWM0_TH51   | 219 |

| 14.2.14 | MCPWM0_TMR0   | 219 |

| 14.2.15 | MCPWM0_TMR1   | 220 |

| 14.2.16 | MCPWM0_TMR2   | 220 |

| 14.2.17 | MCPWM0_TMR3   | 221 |

| 14.2.18 | MCPWM0_TH0    | 221 |

| 14.2.19 | MCPWM0_TH1    | 221 |

| 14.2.20 | MCPWM0_CNT0   | 222 |

| 14.2.21 | MCPWM0_CNT1   | 222 |

| 14.2.22 | MCPWM0_UPDATE | 223 |

| 14.2.23 | MCPWM0_FCNT   | 225 |

| 14.2.24 | MCPWM0_EVT0   | 225 |

| 14.2.25 | MCPWM0_EVT1   | 226 |

| 14.2.26 | MCPWM0_DTH00  | 226 |

| 14.2.27 | MCPWM0_DTH01  | 227 |

| 14.2.28 | MCPWM0_DTH10  | 227 |

| 14.2.29 | MCPWM0_DTH11  | 228 |

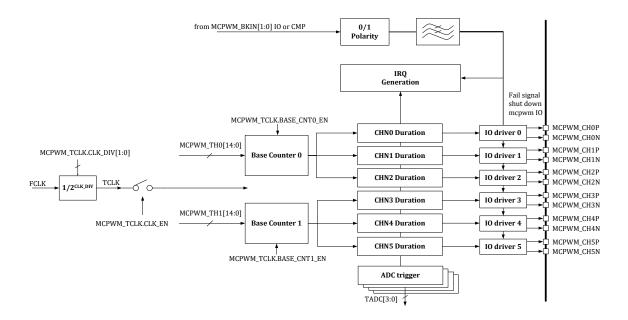

| 14.2.30 | MCPWM0_FLT    | 228 |

| 14.2.31 | MCPWM0_SDCFG  | 228 |

| 14.2.32 | MCPWM0_AUEN   | 229 |

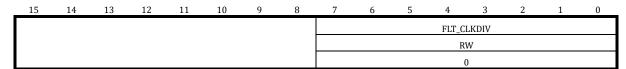

| 14.2.33 | MCPWM0_TCLK   | 230 |

| 14.2.34 | MCPWM0_IE0    | 231 |

| 14.2.35 | MCPWM0_IF0    | 232 |

| 14.2.36 | MCPWM0_IE1    | 233 |

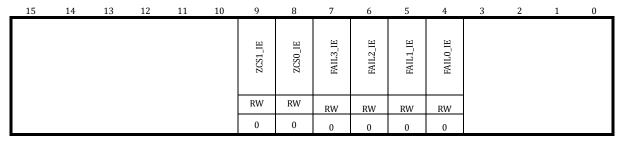

| 14.2.37 | MCPWM0_EIE    | 234 |

| 14.2.38 | MCPWM0_EIF    | 235 |

| 14.2.39 | MCPWMO_RE     | 235 |

| 14.2.40 | MCPWM0_PP     | 236 |

| 14.2.41 | MCPWM0_IO01   | 237 |

| 14.2.42  | MCPWM0_I023              | 238 |

|----------|--------------------------|-----|

| 14.2.43  | MCPWM0_IO45              | 239 |

| 14.2.44  | MCPWM0_IF1               | 240 |

| 14.2.45  | MCPWM0_FAIL012           | 241 |

| 14.2.46  | MCPWM0_FAIL345           | 242 |

| 14.2.47  | MCPWM0_CH_DEF            | 244 |

| 14.2.48  | MCPWM0_CH_MSK            | 244 |

| 14.2.49  | MCPWM0_PRT               | 245 |

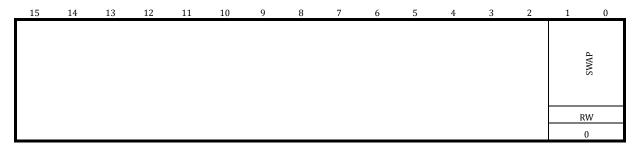

| 14.2.50  | MCPWM0_SWAP              | 246 |

| 14.2.51  | MCPWM0_STT_HYST          | 246 |

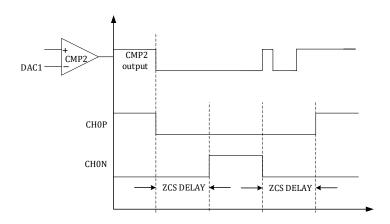

| 14.2.52  | MCPWM0_ZCS_DELAY         | 246 |

| 15 GPIO  |                          | 247 |

| 15.1 OVE | RVIEW                    | 247 |

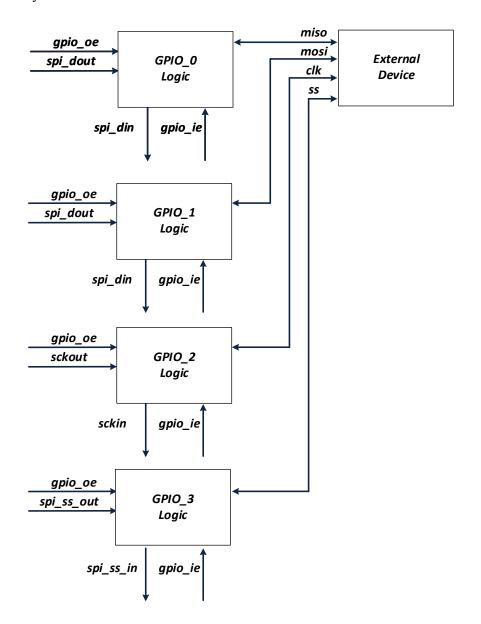

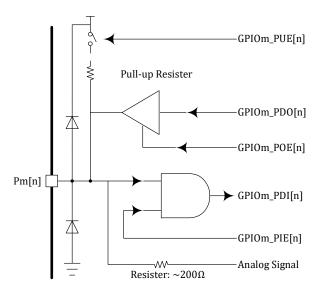

| 15.1.1   | Functional block diagram | 247 |

| 15.1.2   | Product features         | 247 |

| 15.2 REG | iSTER                    | 248 |

| 15.2.1   | Address assignment       | 248 |

| 15.2.2   | GPIOx_PIE                | 249 |

| 15.2.3   | GPIOx_POE                | 250 |

| 15.2.4   | GPIOx_PDI                | 250 |

| 15.2.5   | GPIOx_PDO                | 251 |

| 15.2.6   | GPIOx_PUE                | 251 |

| 15.2.7   | GPIOx_PODE               | 252 |

| 15.2.8   | GPIOx_PFLT               | 253 |

| 15.2.9   | GPIOx_F3210              | 253 |

| 15.2.10  | GPIOx_F7654              | 254 |

| 15.2.11  | GPIOx_FBA98              | 254 |

| 15.2.12  | GPIOx_FFEDC              | 255 |

| 15.2.13  | GPIOx_BSRR               | 255 |

| 15.2.14  | GPIOx_BRR                | 257 |

| 1    | 5.2.15  | External events                         | 257 |

|------|---------|-----------------------------------------|-----|

|      | 15.2.15 | 5.1 EXTI_CRO                            | 257 |

|      | 15.2.15 | 5.2 EXTI_CR1                            | 258 |

|      | 15.2.15 | 5.3 EXTI_IE                             | 260 |

|      | 15.2.15 | 5.4 EXTI_IF                             | 261 |

|      | 15.2.15 | 5.5 CLKO_SEL                            | 262 |

|      | 15.2.15 | 5.6 PWM_SWAP                            | 262 |

| 15.3 | 3 Імрі  | EMENTATION DESCRIPTION                  | 264 |

| 1    | 5.3.1   | Pull-up implementation                  | 264 |

| 1    | 5.3.2   | Filter implementation                   | 264 |

| 1    | 5.3.3   | Pull-up implementation                  | 264 |

| 15.4 | 4 Аррі  | ICATION GUIDE                           | 265 |

| 1    | 5.4.1   | External Interrupt                      | 265 |

| 1    | 5.4.2   | Analog function using GPIO              | 265 |

| 16   | CRC     |                                         | 266 |

| 16.3 | 1 OVE   | RVIEW                                   | 266 |

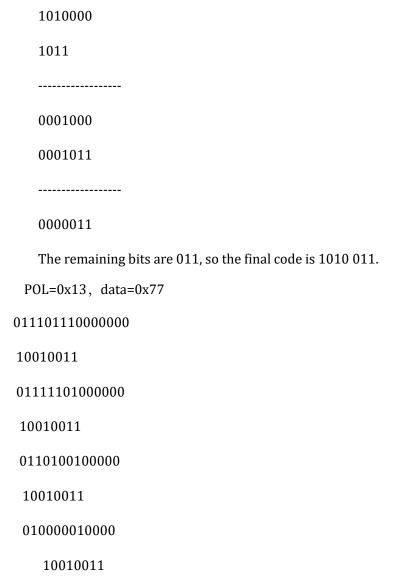

| 16.2 | 2 Basi  | C PRINCIPLES                            | 266 |

| 16.3 | BASI    | C CONCEPTS                              | 266 |

| 1    | 6.3.1   | Correspondence                          | 266 |

| 1    | 6.3.2   | Generator polynomial                    | 267 |

| 1    | 6.3.3   | Number of check code bits               | 267 |

| 1    | 6.3.4   | Generation step                         | 267 |

| 16.4 | 4 Regi  | STER                                    | 269 |

| 1    | 6.4.1   | Address assignment                      | 269 |

| 1    | 6.4.2   | Register description                    | 269 |

|      | 16.4.2. | 1 CRC0_DR CRC information code register | 269 |

|      | 16.4.2. | 2 CRCO_CR CRC Control Register          | 270 |