Linko Semiconductor Co., Ltd. 南京凌鸥创芯电子有限公司

### **Features**

$\circ~$  48MHz 32-bit Cortex-M0 core, hardware division coprocessor

$\circ~$  30uA low-power sleep mode, MCU sleep power consumption is 30uA

$\circ\$  -40-125°C Automotive-grade operating temperature range

$\circ~2.5$  V-5.5 V single power supply, internal integrated digital power supply LDO

$\circ$   $\:$  Super antistatic and anti-group pulse capability

### **Storage**

$\circ~$  32kB flash, with a flash anti-stealing feature  $\circ~$  4kB RAM

### Timer

$\circ~$  Built-in 4MHz high-precision RC timer, with a full temperature range accuracy of  $\pm 2\%$

$\circ~$  Built-in 64kHz low-speed timer for use in low-power mode

$\circ~$  Internal PLL providing up to a 48MHz timer

# Peripherals

- o One UART

- o One SPI

- o One IIC

$\circ~$  General-purpose 16-/32-bit timer, supporting capture and edge-aligned PWM

$\circ~$  Dedicated PWM module for motor control, supporting 6 PWM outputs, independent dead zone control

• Dedicated interface for Hall signals, supporting speed measurement and debounce

- o 4-channel DMA

- Hardware watchdog

- Supports up to 25 GPIOs

### **Analog Module**

$\circ~$  Integrated one 12-bit SAR ADC, 1Msps sampling and conversion rate, 11 channels in total

32bit Compact MCU for Motor Control

Integrated 2 OPA, settable for a differential PGA mode

• Integrated two comparators

• Integrated 8-bit DAC digital-to-analog converter as an internal comparator input

$\circ~$  Built-in 1.2V voltage reference with an accuracy of 0.8%

• Built-in 1 low-power LDO and power monitoring circuit

• Integrated high-precision, low-temperature drift high-frequency RC timer

# **Key Strengths**

♦ The internal integration of 2 high-speed operational amplifiers can meet the different requirements of single-resistor/dual-resistance current sampling topology

♦ The input port of the operational amplifier integrates a voltage clamp protection circuit, and only two external current-limiting resistors are needed to achieve direct current sampling of the MOSFET internal resistance

♦ ADC module variable gain technology can work with high-speed operational amplifiers to handle a wider dynamic range of current and take into account the sampling accuracy of small current and large current

♦ Integrated two-way comparator

♦ Strong ESD and anti-interference ability, stable and reliable

♦ Single power supply 2.5V~5.5V power supply to ensure the versatility of system power supply

♦ Supports IEC/UL60730 functional safety certification

### **Application Scenarios**

Applicable to control systems such as BLDC/ Sensorless BLDC/ FOC/Sensorless FOC and stepping motors, permanent magnet synchronous motors, asynchronous motors, digital power source etc.

# **1** Overview

#### **1.1 Function Description**

LKS32AT037PXL5M6Q9 is a compact MCU with a 32-bit core for automotive electronics applications. It integrates two H-bridge circuits composed of four pairs of P-N power MOSs, which can directly drive three-phase motor windings and stepper motors..

- Performance

- ➢ 48MHz 32-bit Cortex-M0 core

- Low-power sleep mode

- > Integrated three-phase full-bridge bootstrapping gate drive modules

- > Automotive grade operating temperature range

- > Super anti-static and group pulse ability

- ➢ AEC-Q100 Grade1 certified

- Memory

- > 32 kB Flash with encryption, a 128-bit chip unique identifier

- ➢ 4kB RAM

- Operating Range

- > Dual power supply, MCU part adopts 2.5V ~ 5.5V power supply.

- ➢ Operating temperature: -40∼125°C

- Timer

- Built-in 4MHz high-precision RC timer, with an accuracy within ±2% in a range of -40~125°C

- > Built-in 64kHz low-speed timer for use in low-power mode

- > Internal PLL providing up to a 48MHz timer

#### • Peripheral Module

- One UART

- > One SPI for master-slave mode

- > One IIC for master-slave mode

- > One general-purpose 16-bit timer, supporting capture and edge-aligned PWM functions

- > One general-purpose 32-bit timer, supporting capture and edge-aligned PWM functions;

- Dedicated PWM module for motor control, supporting 8 PWM outputs, independent dead zone control

- > Dedicated interface for Hall signals, supporting speed measurement and debounce functions

- Hardware watchdog

- Analog Module

- > Integrated one 12-bit SAR ADC, 1.2Msps sampling and conversion rate, 11 channels in total

- > Integrated a 2-channel operational amplifier, settable for a differential PGA mode

- Integrated two comparators

- > Integrated 8-bit DAC digital-to-analog converter

- Built-in ±2°C temperature sensor

- ▶ Built-in 1.2V voltage reference with an accuracy of 0.8%

- > Built-in 1 low-power LDO and power monitoring circuit

- > Integrated high-precision, low-temperature drift high-frequency RC timer

#### 1.2 Key Strengths

- > High reliability, high integration, small volume of final product, saving BOM costs.

- Internally integrated 2-channel high-speed operational amplifier and two comparators to meet the different requirements of single-resistor/dual-resistor current sampling topologies;

- Internal high-speed operational amplifier integrating high-voltage protection circuits, allowing the high-level common-mode signal to be directly input into the chip, and realizing the direct current sampling mode of MOSFET resistance with the simplest circuit topology;

- The application of patented technology enables the ADC and high-speed operational amplifier to match best, which can handle a wider current dynamic range, while taking into account the sampling accuracy of high-speed small current and low-speed large current;

- The overall control circuit is simple and efficient, with stronger anti-interference ability, more stable and reliable;

- > Integrated three-phase full-bridge bootstrapping gate drive modules;

- ➢ Integrated LIN PHY

- ➢ Integrated 5V LDO

Applicable to control systems such as inductive BLDC/non-inductive BLDC/inductive FOC/non-inductive FOC and stepping motors, permanent magnet synchronous motors, asynchronous motors, etc.;

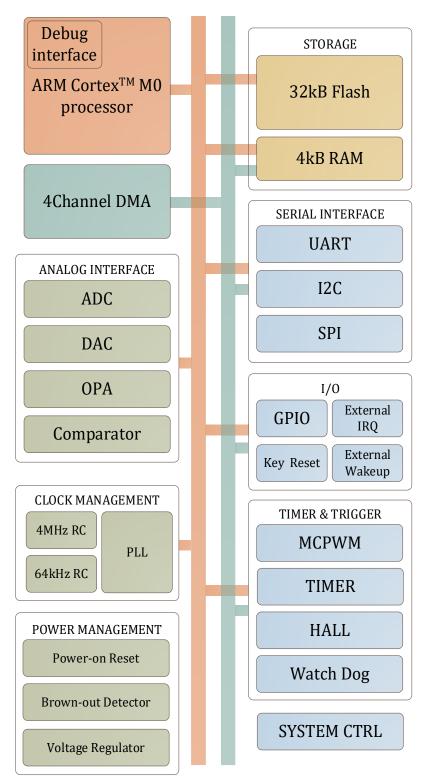

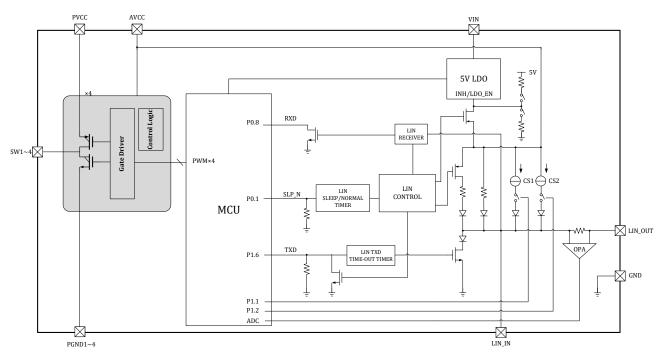

# 1.3 System Resources

Figure 1-1 LKS32AT037PXL5M6Q9 System Block Diagram

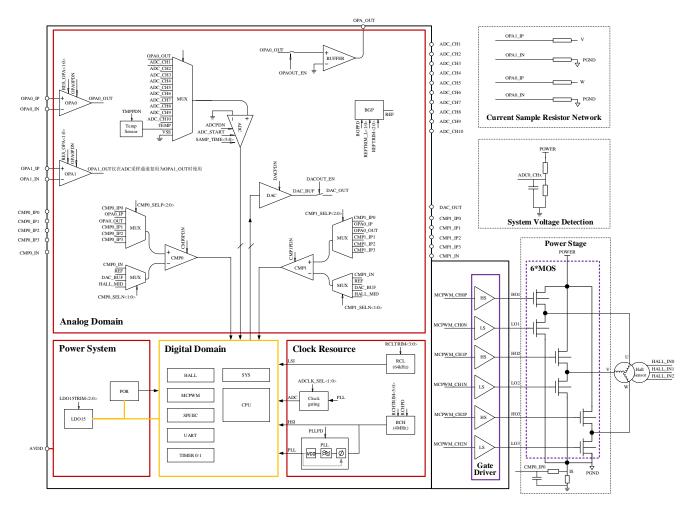

### 1.4 FOC System

Figure 1-2 Simplified Schematic Diagram of the LKS32AT037PXL5M6Q9 Vector Sinusoidal Control System

4

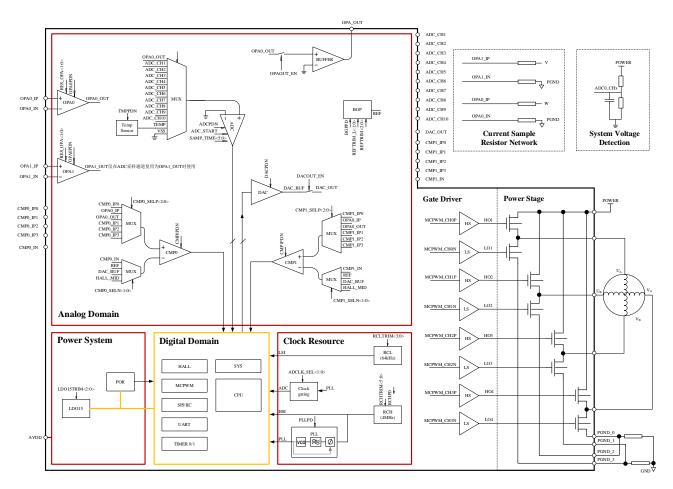

Figure 1-4 Simplified Schematic Diagram of LKS32AT037PXL5M6Q9 Stepper Motor Control System

# 2 Device Selection Table

|                     | Frequency (MHz) | Flash (kB) | RAM (kB) | ADC ch. | DAC    | Comparator | Comparator ch. | OPA | HALL | IdS | IIC | UART | CAN | Temp. Sensor | Tria | QEP | Gate driver | Gate Driver current (A) | Pre-drive supply (V) | Gate floating voltage (V) | Others | Package |

|---------------------|-----------------|------------|----------|---------|--------|------------|----------------|-----|------|-----|-----|------|-----|--------------|------|-----|-------------|-------------------------|----------------------|---------------------------|--------|---------|

| LKS32AT037PXL5M6Q9* | 48              | 32         | 4        | 10      | 8BITx1 | 2          | 8              | 2   | 3    | 1   | 1   | 1    |     | Yes          | Yes  |     |             |                         |                      |                           | 5V LDO | QFN24   |

#### Table 2-1 LKS32AT037PXL5M6Q9 Series Device Selection Table

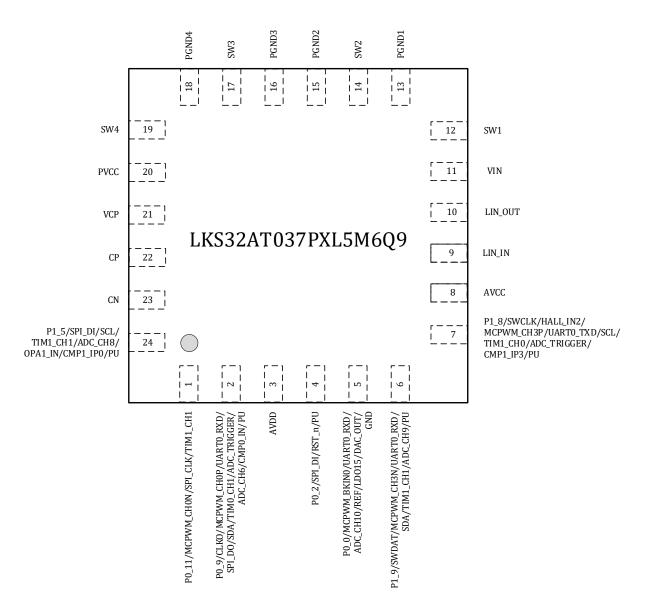

### 3 Pin Assignment

#### 3.1 Pin Assignment Diagram

#### 3.1.1 Special Notes

PU is short for pull-up. The PU pin in the following pin diagrams is designed with an internal pull-up resistor to the AVDD.

The RSTN pin is equipped with an internal  $100k\Omega$  pull-up resistor that is fixed to turn on the pull-up, which can be turned off when the RSTN function is switched to the GPIO function

The SWDIO/SWCLK has a built-in 10kΩ pull-up resistor. The pull-up is fixed on. When the SWD function is switched to the GPIO function, the pull-up can be turned off. Since SWDIO/SWCLK is connected to the drive of the internal MOS, SWDIO/SWCLK cannot communicate when PVDD (MOS power supply) is on.

The remaining PU pins have an internal  $10k\Omega$  pull-up resistor that can be turned on or off by software control.

EXTI is external interrupt or GPIO interrupt input pin.

WK is short for wake-up, is external wake-up source.

UARTx\_TX(RX): UART supports an interchange between the TX and RX. When the second function of GPIO is selected as UART and GPIO\_PIE i.e. input is enabled, it can be used as UART\_RX; When GPIO\_POE is enabled, it can be used as UART\_TX. Generally, the same GPIO does not enable input and output at the same time, otherwise the input PDI will receive the data sent by the PDO.

SPI\_DI(DO): The DI and DO of SPI can be interchanged. When the second function of GPIO is SPI, and GPIO\_PIE i.e. input is enabled, it can be used as SPI\_DI; when GPIO\_POE i.e. output is enabled, it can be used as SPI\_DO. Generally, the same GPIO does not enable input and output at the same time, otherwise the input PDI will receive the data sent by the PDO.

### 3.1.2 LKS32AT037PXL5M6Q9

Figure 3-1 LKS32AT037PXL5M6Q9 Pin Assignment Diagram

| 0 | AGND       | Ground                 |

|---|------------|------------------------|

|   | P0_11      | P0.11                  |

| 1 | MCPWM_CH0N | PWM channel 0 low-side |

| 1 | SPI_CLK    | SPI clock              |

|   | TIM1_CH1   | Timer1 channel1        |

| 2 | P0_9       | P0.9                   |

| Z | CLKO       | Clock output for debug |

Table 3-1 LKS32AT037PXL5M6Q9 Pin description

|   | MCPWM_CH0P      | PWM channel 0 high-side                                                                    |

|---|-----------------|--------------------------------------------------------------------------------------------|

|   | UARTO_RXD       | UART0 receive(transmit)                                                                    |

|   | <br>SPI_DO      | SPI data output(input)                                                                     |

|   | SDA             | I2C data                                                                                   |

|   | TIM0_CH1        | Timer0 channel1                                                                            |

|   | <br>ADC_TRIGGER | ADC trigger for debug                                                                      |

|   | ADC_CH6         | ADC channel 6                                                                              |

|   | CMP0_IN         | Comparator0 negative input                                                                 |

|   | PU              | Built-in $10k\Omega$ Pull-up resistor which could be turn-off by software                  |

|   | EXTI7           | External GPIO Interrupt Signal 7                                                           |

|   | WK3             | External wake-up signal 3                                                                  |

| 3 | AVDD            | Power supply, 2.2~5.5V                                                                     |

| - | P0_2            | P0.2                                                                                       |

|   | SPI_DI          | SPI data input(output)                                                                     |

|   |                 | P0.2 is used as RSTN by default. A 10nF-100nF capacitor should be connected to the         |

|   |                 | ground. It is recommended a 10k-20k pull-up resistor is placed between RSTN and AVDD       |

| 4 | RST_n           | on PCB. If there is an external pull-up resistor, the capacitance of RSTN should be 100nF. |

| 1 |                 | The built-in $10k\Omega$ pull-up resistor could be turned-off by software.                 |

|   | PU              | Built-in $10k\Omega$ Pull-up resistor which could be turn-off by software                  |

|   | EXTI1           | External GPIO Interrupt Signal 1                                                           |

|   | WK1             | External wake-up signal 1                                                                  |

|   | P0_0            | P0.0                                                                                       |

|   | MCPWM_BKIN0     | PWM break signal 0                                                                         |

|   | UARTO_RXD       | UARTO receive(transmit)                                                                    |

|   | ADC_CH10        | ADC channel 10                                                                             |

| 5 | REF             | Reference voltage output for debug                                                         |

| 5 | LD015           | 1.5V LDO output                                                                            |

|   | DAC_OUT         | DAC output                                                                                 |

|   | EXTIO           | External GPIO Interrupt Signal 0                                                           |

|   | WK0             | External wake-up signal 0                                                                  |

|   | P1_9            | P1.9                                                                                       |

|   | SWDAT           | SWD Data                                                                                   |

|   | MCPWM_CH3N      | PWM channel 3 low-side                                                                     |

|   |                 |                                                                                            |

|   | UARTO_RXD       | UARTO receive(transmit) I2C data                                                           |

| 6 | SDA             | Timer1 channel1                                                                            |

|   | TIM1_CH1        |                                                                                            |

|   | ADC_CH9         | ADC channel 9 Puilt in 10kO. Pull up register which could be turn off by coffuere          |

|   | PU              | Built-in $10k\Omega$ Pull-up resistor which could be turn-off by software                  |

|   | EXTI15          | External GPIO Interrupt Signal 15                                                          |

|   | WK7             | External wake-up signal 7                                                                  |

| _ | P1_8            | P1.8                                                                                       |

| 7 | SWCLK           | SWD Clock                                                                                  |

|   | HALL_IN2        | Hall interface input 2                                                                     |

|    | MCPWM_CH3P  | PWM channel 3 high-side                                                                |

|----|-------------|----------------------------------------------------------------------------------------|

|    | UARTO_TXD   | UARTO transmit(receive)                                                                |

|    | SCL         | I2C clock                                                                              |

|    | TIM1_CH0    | Timer1 channel0                                                                        |

|    | ADC_TRIGGER | ADC trigger for debug                                                                  |

|    | CMP1_IP3    | Comparator1 positive input3                                                            |

|    | PU          | Built-in $10k\Omega$ Pull-up resistor which could be turn-off by software              |

|    | EXTI14      | External GPIO Interrupt Signal 14                                                      |

|    | WK6         | External wake-up signal 6                                                              |

| 8  | AVCC        | IPM Analog Power Supply Input, LIN PHY power supply                                    |

| 0  | nvou        | LIN bus input, transmitting via MCU P1.6 UARTO _ TXD function, receiving and wake-up   |

| 9  | LIN_IN      | via MCU P0.8 UART0 _ TXD/WK2 function                                                  |

| 10 | LIN_OUT     | LIN bus output                                                                         |

| 11 | VIN         | 5V LDO power input.                                                                    |

|    | V III       | The first phase output is controlled by MCPWM_CH0P of MCU P0.10. When PWM1 = 1, the    |

| 12 | SW1         | upper transistor is on, the lower transistor is off, and the output SW = $1$           |

| 13 | PGND1       | Phase 1 power ground                                                                   |

|    |             | The second phase output is controlled by MCPWM _ CH1N of MCU P0.4. When PWM 1 = 1,     |

| 14 | SW2         | the upper transistor is on, the lower transistor is off, and the output SW = $1$       |

| 15 | PGND2       | Phase 2 power ground                                                                   |

| 16 | PGND3       | Phase 3 power ground                                                                   |

|    |             | The third phase output is controlled by MCPWM _ CH2N of MCU P0.15. When PWM 1 = 1,     |

| 17 | SW3         | the upper transistor is on, the lower transistor is off, and the output SW = 1.        |

| 18 | PGND4       | Phase 4 power ground                                                                   |

| -  |             | 4th phase output, controlled by MCPWM _ CH3P of MCU P0.3, when PWM 1 = 1, the upper    |

| 19 | SW4         | transistor is on, the lower transistor is off, and the output SW = 1                   |

|    |             | MOS power supply input, it is recommended to place a 10 uF decoupling capacitor nearby |

| 20 | PVCC        | to ground                                                                              |

| 21 | VCP         | Charge Pump Output                                                                     |

| 22 | СР          | Charge-pumped flying-capacitor top plate                                               |

| 23 | CN          | Charge-pumped flying-capacitor bottom plate                                            |

|    | P1_5        | P1.5                                                                                   |

|    | SPI_DI      | SPI data input(output)                                                                 |

|    | SCL         | I2C clock                                                                              |

|    | TIM1_CH1    | Timer1 channel1                                                                        |

| 24 | ADC_CH8     | ADC channel 8                                                                          |

| 24 | OPA1_IN     | OPA1 negative input                                                                    |

|    | CMP1_IP0    | Comparator1 positive input0                                                            |

|    | PU          | Built-in $10k\Omega$ Pull-up resistor which could be turn-off by software              |

|    | EXTI11      | External GPIO Interrupt Signal 11                                                      |

|    | WK5         | External wake-up signal 5                                                              |

| Table 3-2 LKS32AT037PXL5M6Q9 Desc | rintion of internal channel relationshin |

|-----------------------------------|------------------------------------------|

| Table 5-2 LISSZATOS/TALSMOQ9 Desc |                                          |

| MCUPin definitions                                                                            | Internal signal function | Description                                                                                              |

|-----------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|

| P1_4/CMP1_OUT/MCPWM_BKIN0                                                                     | FO                       | IPM fault output.When the IPM fails, pull                                                                |

| /SPI_CS/TIM0_CH1/CMP1_IN/PU/EXTI1                                                             | FO                       | the signal high                                                                                          |

| P1_1/OPA0_IP                                                                                  | CS1                      | Control signal of current source 1 in BSM                                                                |

|                                                                                               | 651                      | addressing mode                                                                                          |

| P1_2/OPA0_IN                                                                                  | CS2                      | Control signal of current source 2 in BSM                                                                |

|                                                                                               | 002                      | addressing mode                                                                                          |

| P0_0/MCPWM_BKIN0/UART0_RXD/ADC_CH10/R<br>EF/LD015/DAC_OUT/EXTI0/WK0                           | VSMP1                    | Voltage detection channel 1                                                                              |

| P0_5/HALL_IN1/MCPWM_BKIN1/UART0_TXD/SD<br>A/TIM1_CH1 /ADC_CH2/CMP0_IP1/PU/EXTI3               | VSMP2                    | Voltage detection channel 2                                                                              |

| P0_6/HALL_IN2/ADC_CH3 /CMP0_IP0/EXTI                                                          | CSMP1                    | Voltage detection channel 1                                                                              |

| P0_7/UART0_TXD/SCL/TIM0_CH1/ADC_CH5/OPA<br>x_OUT/PU/EXTI                                      | CSMP2                    | Voltage detection channel 2                                                                              |

| P0_10/CLKO/MCPWM_CH0P/TIM0_CH0/TIM1_C<br>H0                                                   | SW1                      | PWM Input for SW1                                                                                        |

| P0_4/HALL_IN0/MCPWM_CH1N/UART0_RXD/SPI                                                        |                          |                                                                                                          |

| _CS/SCL/TIM1_CH0/ADC_TRIGGER/ADC_CH1/CM                                                       | SW2                      | PWM Input for SW2                                                                                        |

| P0_IP2/PU/EXTI2                                                                               |                          |                                                                                                          |

| P0_15/MCPWM_CH2N /TIM1_CH0/EXT9                                                               | SW3                      | PWM Input for SW3                                                                                        |

| P0_3/TIM1_CH0 /OPA0_IN_B                                                                      | SW4                      | PWM Input for SW4                                                                                        |

| P1_3/SPI_CS /TIM1_CH0/OPA1_IP                                                                 | SPI_CS                   | Chip select signal of SPI bus                                                                            |

| 1_7/CMP0_OUT/HALL_IN0/MCPWM_CH2P/UART<br>0_RXD/TIM0_CH0/ADC_TRIGGER<br>/CMP1_IP1/PU/EXTI13    | SPI_CL                   | Clock signal of SPI bus                                                                                  |

| P0_13/MCPWM_CH1N /SPI_DI/TIM1_CH1                                                             | SPI_MISO                 | Data line of SPI bus, IPM output, MCU in-<br>put                                                         |

| P0_12/MCPWM_CH1P /SPI_DO/TIM0_CH1                                                             | SPI_MOSI                 | Data line of SPI bus, MCU output, IPM in-<br>put                                                         |

| P0_1/SPI_CS / OPA0_IP_B                                                                       | SLP_N                    | Enable input port, high enable device en-<br>ters normal mode, low disable device en-<br>ters sleep mode |

| P0_8/CMP0_OUT/MCPWM_BKIN1/UART0_TXD/S<br>PI_CLK/SCL/TIM0_CH0/ADC_TRIGGER<br>/ADC_CH4/CMP0_IP3 | RXD                      | Receiver data output (open-drain) port;<br>held low after a wake-up event.                               |

| P1_6/CMP1_OUT/HALL_IN1/MCPWM_CH2N/UAR<br>T0_TXD/TIM0_CH1/ADC_TRIGGER/ADC_CH7/CM<br>P1_IP2     | TXD                      | LIN Transmitter Data Input Port                                                                          |

### 3.2 Pin Multiplexing

| Port  | AF1      | AF2      | AF3         | AF4          | AF5        | AF6 | AF7      | AF8        | AF9         | AF0                        |

|-------|----------|----------|-------------|--------------|------------|-----|----------|------------|-------------|----------------------------|

| P0.0  |          |          | MCPWM_BKIN0 | UART0_R(T)XD |            |     |          |            |             | ADC_CH10/REF/LD015/DAC_OUT |

| P0.1  |          |          |             |              | MCPWM_CH3N |     |          |            |             | OPA0_IP_B                  |

| P0.2  |          |          |             |              | SPI_DI(O)  |     |          |            |             | RST_n                      |

| P0.3  |          |          |             |              |            |     |          | MCPWM_CH3P |             | OPA0_IN_B                  |

| P0.4  |          | HALL_IN0 | MCPWM_CH1N  | UART0_R(T)XD | SPI_CS     | SCL |          | TIM1_CH0   | ADC_TRIGGER | ADC_CH1/CMP0_IP2           |

| P0.5  |          | HALL_IN1 | MCPWM_BKIN1 | UART0_T(R)XD |            |     |          | TIM1_CH1   |             | ADC_CH2/CMP0_IP1           |

| P0.6  |          | HALL_IN2 |             |              |            |     |          |            |             | ADC_CH3/CMP0_IP0           |

| P0.7  |          |          |             | UART0_T(R)XD |            | SCL | TIM0_CH1 |            |             | ADC_CH5/OPAx_OUT           |

| P0.8  | CMP0_OUT |          | MCPWM_BKIN1 | UART0_T(R)XD | SPI_CLK    | SCL | TIM0_CH0 |            | ADC_TRIGGER | ADC_CH4/CMP0_IP3           |

| P0.9  | CLKO     |          | MCPWM_CH0P  | UART0_R(T)XD | SPI_DO(I)  | SDA | TIM0_CH1 |            | ADC_TRIGGER | ADC_CH6/CMP0_IN            |

| P0.10 | CLKO     |          | MCPWM_CH0P  |              |            |     | TIM0_CH0 | TIM1_CH0   |             |                            |

| P0.11 |          |          | MCPWM_CH0N  |              | SPI_CLK    |     |          | TIM1_CH1   |             |                            |

| P0.12 |          |          | MCPWM_CH1P  |              | SPI_DO(I)  |     | TIM0_CH1 |            |             |                            |

| P0.13 |          |          | MCPWM_CH1N  |              | SPI_DI(O)  |     |          | TIM1_CH1   |             |                            |

| P0.14 |          |          | MCPWM_CH2P  |              |            |     | TIM0_CH0 |            |             |                            |

| P0.15 |          |          | MCPWM_CH2N  |              |            |     |          | TIM1_CH0   |             |                            |

#### Table 3-2 LKS32AT037PXL5M6Q9 Pin Function Selection

#### LKS32AT037PXL5M6Q9

| Port | AF1      | AF2      | AF3         | AF4          | AF5       | AF6 | AF7      | AF8      | AF9         | AF0                      |

|------|----------|----------|-------------|--------------|-----------|-----|----------|----------|-------------|--------------------------|

| P1.1 |          |          |             |              |           |     |          |          |             | OPA0_IP                  |

| P1.2 |          |          |             |              |           |     |          |          |             | OPA0_IN                  |

| P1.3 |          |          |             |              | SPI_CS    |     |          | TIM1_CH0 |             | OPA1_IP                  |

| P1.4 | CMP1_OUT |          | MCPWM_BKIN0 |              | SPI_CS    |     | TIM0_CH1 |          |             | CMP1_IN                  |

| P1.5 |          |          |             |              | SPI_DI(O) | SCL |          | TIM1_CH1 |             | ADC_CH8/OPA1_IN/CMP1_IP0 |

| P1.6 | CMP1_OUT | HALL_IN1 | MCPWM_CH2N  | UART0_T(R)XD |           |     | TIM0_CH1 |          | ADC_TRIGGER | ADC_CH7/CMP1_IP2         |

| P1.7 | CMP0_OUT | HALL_IN0 | MCPWM_CH2P  | UART0_R(T)XD |           |     | SPI_CLK  |          | ADC_TRIGGER | CMP1_IP1                 |

| P1.8 | SWCLK    | HALL_IN2 | MCPWM_CH3P  | UART0_T(R)XD |           | SCL |          | TIM1_CH0 | ADC_TRIGGER | CMP1_IP3                 |

| P1.9 | SWDAT    |          | MCPWM_CH3N  | UART0_R(T)XD |           | SDA |          | TIM1_CH1 |             | ADC_CH9                  |

# 4 Package Dimensions

### 4.1 LKS32AT037PXL5M6Q9

QFN24(4\*4) Profile Quad Flat Package:

Package Top View

Package Bottom View

Package Side View

### Figure 4-1 LKS32AT037PXL5M6Q9 Packaging

| Table 4-2 LK352AT05/FALSM0Q9 Fackaging Dimensions |          |       |       |  |  |  |  |  |  |

|---------------------------------------------------|----------|-------|-------|--|--|--|--|--|--|

| CVMDOI                                            | MLLMETER |       |       |  |  |  |  |  |  |

| SYMBOL                                            | MIN      | NOM   | MAX   |  |  |  |  |  |  |

| А                                                 | 0.500    | 0.550 | 0.600 |  |  |  |  |  |  |

| A1                                                | 0.007    | 0.012 | 0.017 |  |  |  |  |  |  |

| D                                                 | 3.90     | 4.00  | 4.10  |  |  |  |  |  |  |

| Е                                                 | 3.90     | 4.00  | 4.10  |  |  |  |  |  |  |

| D1                                                | 2.250    | 2.300 | 2.350 |  |  |  |  |  |  |

| E1                                                | 1.950    | 2.000 | 2.050 |  |  |  |  |  |  |

| L                                                 | 0.300    | 0.350 | 0.400 |  |  |  |  |  |  |

| b                                                 | 0.20     | 0.25  | 0.30  |  |  |  |  |  |  |

| е                                                 | 0.500    | 0.550 | 0.600 |  |  |  |  |  |  |

| X1                                                | 0.450    | 0.500 | 0.550 |  |  |  |  |  |  |

| X2                                                | 0.750    | 0.800 | 0.850 |  |  |  |  |  |  |

| Х3                                                | 0.450    | 0.500 | 0.550 |  |  |  |  |  |  |

#### Table 4-2 LKS32AT037PXL5M6Q9 Packaging Dimensions

# **5** Electrical Characteristics

The LKS32AT037PXL5M6Q9 chip is internally integrated with 8N MOS, and the electrical parameters of MCU are shown in the following table

# 5.1 Limit parameters

| Parameter                            | Min  | Max   | Unit | Description                                                                                                               |

|--------------------------------------|------|-------|------|---------------------------------------------------------------------------------------------------------------------------|

| MCU power sup-<br>ply(AVDD)          | -0.3 | +6.0  | v    |                                                                                                                           |

| IDM Dowor gupply yelt                | -0.3 | +40.0 | V    | Limiting short-time working voltage t <500ms                                                                              |

| IPM Power supply volt-<br>age (PVCC) | -150 | 100   | V    | Limit pulse voltage, peripheral TVS and re-<br>verse diode protection                                                     |

| V <sub>LIN</sub>                     | -40  | 40    | V    | Limiting pulse voltage, Reference<br>ISO7637-2-2011                                                                       |

| IPMAnalog Supply Volt-<br>age (AVCC) | -0.3 | +40.0 | V    | Limiting short-time working voltage t <500ms                                                                              |

| IPM MOSFET current                   | -2.0 | +2.0  | A    | More than 800 mA requires careful heat dis-<br>sipation to ensure that the die junction tem-<br>perature is below 150 ° C |

| 5V LDO Output current                |      | 50    | mA   |                                                                                                                           |

| Operating temperature                | -40  | +125  | °C   |                                                                                                                           |

| Storage temperature                  | -55  | +150  | °C   |                                                                                                                           |

| Junction temperature                 | -    | 150   | °C   |                                                                                                                           |

| Pin temperature                      | -    | 300   | °C   | Welding, 10 seconds                                                                                                       |

Table 5-1 LKS32AT037PXL5M6Q9 Electrical Limit Parameter

If AVCC and PVCC are directly connected on the system, AVCC shall consider the same limit conditions.

Table 5-2 LKS32AT037PXL5M6Q9I0 Limit parameter

| Parameter            | Description                            | Min   | Max  | Unit |

|----------------------|----------------------------------------|-------|------|------|

| V <sub>IN-LIN</sub>  | LIN pin input voltage range            | -58   | 58   | V    |

| V <sub>IN</sub>      | GPIO signal input voltage range        | -0.3  | 6.0  | V    |

| I <sub>INJ_PAD</sub> | Single GPIO Maximum Injection Current  | -11.2 | 11.2 | mA   |

| I <sub>INJ_SUM</sub> | Maximum injection current of all GPIOs | -50   | 50   | mA   |

### 5.2 Recommended operating conditions

Table 5-3 LKS32AT037PXL5M6Q9 Recommended Operating Conditions

| Parameter                 | Min | Тур | Max | Unit | Description |

|---------------------------|-----|-----|-----|------|-------------|

| MCU Supply voltage (AVDD) | 2.5 | 5   | 5.5 | V    |             |

| Analog operating voltage            | 2.8 | 5 | 5.5 | V | REF2VDD=0, ADC Selects 2.4V Inter-<br>nal Reference |

|-------------------------------------|-----|---|-----|---|-----------------------------------------------------|

| (AVDD <sub>A</sub> )                | 2.4 | 5 | 5.5 | V | REF2VDD=1, ADC selects AVDD as reference            |

| IPM Power supply voltage<br>(PVCC)  | 8   |   | 28  | V |                                                     |

| IPM Analog Supply Voltage<br>(AVCC) | 8   |   | 28  | V |                                                     |

OPA could work under 2.5V, but the output range will be limited.

### 5.3 ESD performance

| Project                        | Min   | Max   | Unit |

|--------------------------------|-------|-------|------|

| ESD test(HBM) LIN Pin, MCU Pin | -6000 | +6000 | V    |

| ESD test(HBM) other Pins       | -2000 | +2000 | V    |

| ESD test(CDM)                  | -500  | +500  | V    |

According to "MIL-STD-883J Method 3015.9", under the environment of 25°C and 55% relative humidity, electrostatic discharge is applied to all IO pins of the tested chip for 3 times, with an interval of 1s each time. The test results show that the anti-static discharge level of the chip reaches Class  $3A \ge 4000V$ , <8000V.

#### Table 5-5 LKS32AT037PXL5M6Q9 Latch-up parameters

| Project                                | Min  | Max  | Unit |

|----------------------------------------|------|------|------|

| LIN/MOS output Latch-up current (25°C) | -300 | +300 | mA   |

| other IO Latch-up current (25°C)       | -200 | +200 | mA   |

According to "JEDEC STANDARD NO.78E NOVEMBER 2016", apply an overvoltage of 8V to all power IOs and inject 200mA of current on each signal IO. The test results show that the anti-latch-up level of the chip is 200mA.

# 5.4 IO characteristics

| Pa-<br>rame-<br>ter | Description                                  | AVDD | Condition | Min.     | Max.     | Unit |

|---------------------|----------------------------------------------|------|-----------|----------|----------|------|

| V <sub>IH</sub>     | Digital IO Input High Voltage                | 5V   | _         | 0.7*AVDD |          | V    |

| V IH                | Digital 10 input ingli voltage               | 3.3V |           | 2.0      |          | v    |

| V                   | V <sub>IL</sub> Digital IO Input Low Voltage |      |           |          | 0.3*AVDD | v    |

| V IL                |                                              |      | -         |          | 0.8      | v    |

#### Table 5-6 LKS32AT037PXL5M6Q9 IO DC Parameter

| 17                                             |                                           | 5V   |                | 0.1*4000  |     | V  |

|------------------------------------------------|-------------------------------------------|------|----------------|-----------|-----|----|

| V HYS                                          | V <sub>HYS</sub> Schmidt hysteresis range |      | -              | 0.1*AVDD  |     | v  |

| т                                              | Digital IO input high voltage,            | 5V   |                |           | 1   | ۸  |

| I <sub>IH</sub>                                | current consumption                       | 3.3V | -              |           | Ţ   | uA |

| I.,                                            | Digital IO input low voltage,             | 5V   |                | -1        |     | uA |

| I <sub>IL</sub>                                | current consumption                       | 3.3V | -              | -1        |     | uA |

| V <sub>OH</sub> Digital IO Output High Voltage |                                           |      | Maximum drive  | AVDD-0.8  |     | v  |

| V OH                                           | Digital 10 Output High Voltage            |      | current 11.2mA | AV DD-0.0 |     | v  |

| Vol                                            | Digital IO Output Low Voltage             |      | Maximum drive  |           | 0.5 | v  |

| VOL                                            | Digital 10 Output Low Voltage             |      | current 11.2mA |           | 0.5 | v  |

| $R_{pup}$                                      | Pull-up resistor size *                   |      |                | 8         | 12  | kΩ |

| п                                              | Connection resistance between             |      |                | 100       | 200 | 0  |

| R <sub>io-ana</sub>                            | IO and internal analog circuit            |      |                | 100       | 200 | Ω  |

| C <sub>IN</sub>                                | Digital IO input capacitance              | 5V   | -              |           | 10  | pF |

\* Only part of IOs have built-in pull-up resistors. Please refer to the pin description section for details

### **5.5 IPM parameters**

| Parameter                        | Min. | Тур. | Max. | Unit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output current (Iout_Pk)         |      | 0.8  | 2.0  | А    | VIN=16V, $I_{out_Pk} = 0.81A$ , $Tc = 125^{\circ}C$ ,<br>At this time, the chip $T_j = 145^{\circ}C$ ; PCB<br>double-layer board, the board thick-<br>ness is 1.6mm, the copper thickness is<br>1 oz, and the pad size refers to the<br>package size or demo board in Section<br>4; $I_{OUT_Pk} = 2.0$ A. The duration is<br>mainly related to the heat dissipation<br>of the chip, and the junction tempera-<br>ture of the MCU shall be kept within<br>150 °C.<br>The chip can support driving BLDC<br>motors with a phase current RMS of<br>1A at a maximum ring temperature of<br>105 degrees. |

| On impedance (R <sub>DSON)</sub> |      | 0.5  | 0.8  | Ω    | Upper bridge + lower bridge, VCC =<br>12V~24V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Table 5-8 LKS32AT037PXL5M6Q9 IPM Back EMF detection

| Parameter | Min. | Тур. | Max. | Unit | Description                         |

|-----------|------|------|------|------|-------------------------------------|

| Remf_pu   | 110  | 140  | 170  | kΩ   | Back-EMF detection pull-up resistor |

| Rbemf_pd | 8    | 10 | 12   | kΩ  | Back-EMF detection pull-down resis-<br>tor                |

|----------|------|----|------|-----|-----------------------------------------------------------|

| Reemf    | 14.5 | 15 | 15.5 | V/V | Counter electromotive force voltage division output ratio |

### Table 5-9 LKS32AT037PXL5M6Q9 IPM VCP Charge pump

| Parameter | Min. | Тур. | Max.    | Unit | Description                       |          |

|-----------|------|------|---------|------|-----------------------------------|----------|

| Vcp       | 4.9  | 5.2  | 5.5     | V    | Charge Pump Output Voltage,       |          |

| VCP       | 4.9  | 5.2  | 4.9 5.2 | 5.5  | V                                 | VCP-PVCC |

| Іср       | 2.0  |      |         | m۸   | Charge pump load current to meet  |          |

| ICP       | 2.0  |      |         | mA   | output voltage requirement        |          |

| ICP_LIM   | 10   |      |         | mA   | Charge Pump Output Current Limit  |          |

| Vср_ок    | 4.45 | 4.6  | 4.85    | V    | VCP Undervoltage release point    |          |

| VCP_Hyst  | 4.1  | 4.3  | 4.5     | V    | VCP Undervoltage protection point |          |

| VCP_Hys   |      | 0.3  |         | V    | VCP Undervoltage hysteresis       |          |

Table 5-10 LKS32AT037PXL5M6Q9 IPM Over-temperature protection

| Parameter | Min. | Тур. | Max. | Unit | Description                                                                                                          |

|-----------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------|

|           | 140  | 150  | 160  | °C   | Over-temperature protection thresh-<br>old, OTP = 2'b00 Gear, Refer to the<br>user manual for specific configuration |

| Тотр      | 120  | 130  | 140  | °C   | Over-temperature protection thresh-<br>old, OTP = 2'b01 Gear                                                         |

|           | 155  | 170  | 185  | °C   | Over-temperature protection thresh-<br>old, OTP = 2'b10 Gear                                                         |

|           | 110  | 120  | 130  | °C   | Over-temperature protection thresh-<br>old, OTP = 2'b00 Gear                                                         |

| Totp_Rel  | 90   | 100  | 110  | °C   | Over-temperature protection thresh-<br>old, OTP = 2'b01 Gear                                                         |

|           | 130  | 140  | 150  | °C   | Over-temperature protection thresh-<br>old, OTP = 2'b10 Gear                                                         |

#### Table 5-9 LKS32AT037PXL5M6Q9 Consumption IDDQ

| Clock | Operating mode                                                                        | 3.3V  | 5V    | Unit |

|-------|---------------------------------------------------------------------------------------|-------|-------|------|

| 48MHz | CPU, flash, SRAM, MCPWM, Timer, and all analog mod-<br>ules are active, IOs stay idle | 8.570 | 8.650 | mA   |

| 4MHz  | CPU, flash, SRAM, MCPWM, Timer, and all analog mod-                                   | 3.012 | 3.165 | mA   |

| 64kHz | ules except PLL are active, IOs stay idle                                             | 2.445 | 2.618 | mA   |

| -     | Deep Sleep Mode, PLL and BGP are turned off, only<br>64kHz LRC is running             | 27    | 30    | uA   |

| -     | All analog modules                                                                    | 2.4   | 2.55  | mA   |

### 5.6 Sleep Power Consumption

| Parameter                            | TE                                                   | Min                     | Typical | Max | Unit |    |  |  |

|--------------------------------------|------------------------------------------------------|-------------------------|---------|-----|------|----|--|--|

| I <sub>BAT</sub> (V <sub>BAT</sub> ) | Quiescent m                                          | 3                       | 10      | 20  | μA   |    |  |  |

| MOS(PVDD)                            | V <sub>WAKE_N</sub> =V <sub>BAT</sub> V <sub>T</sub> |                         | 280     |     | μA   |    |  |  |

|                                      | Quiagant                                             | I <sub>OUT</sub> =0mA   |         | 3   | 5.5  | μA |  |  |

| 5V LDO(VIN)                          | Quiescent                                            | I <sub>OUT</sub> =0.1mA |         | 4   | 6.5  | μA |  |  |

|                                      | Shutdown                                             | $V_{EN}=0V$             |         | 0.4 | 2    | μA |  |  |

#### Table 5-10 LKS32AT037PXL5M6Q9 Sleep power consumption

Unless otherwise specified, the above tests are all measured at room temperature of 25°. Due to the deviation of the device model in the manufacturing process, the current consumption of different chips will have individual differences.

#### 5.7 Automatic addressing correlation

| Parameter                                          | Min. | Тур. | Max. | Unit | Description                                                                                                                                                                                                                                                                    |

|----------------------------------------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{on\_cs}$ Current source on time                |      |      | 5    | us   |                                                                                                                                                                                                                                                                                |

| $t_{off\_cs}$ Current source off time              |      |      | 1    | us   |                                                                                                                                                                                                                                                                                |

| I <sub>cs1</sub>                                   | 1    |      | 1.24 | mA   | BSM Current in addressing mode1                                                                                                                                                                                                                                                |

| I <sub>cs2</sub>                                   | 3.15 |      | 3.85 | mA   | BSM Current in addressing mode2                                                                                                                                                                                                                                                |

| Differential Error Ampli-<br>fier Closed-Loop Gain | 62   | 64   | 65   | V/V  |                                                                                                                                                                                                                                                                                |

| R <sub>shunt</sub> LIN Bus series re-<br>sistance  | 1    | 1.5  | 2    | Ω    | Internal integration                                                                                                                                                                                                                                                           |

| I <sub>diff</sub>                                  | 2.3  |      | 2.9  | mA   | The current threshold on R <sub>shunt</sub> when<br>the current source CS1 is closed. If it<br>exceeds the threshold, it is considered<br>not to be the farthest node candidate<br>and will not participate in the next<br>round of current measurement and<br>identification. |

Table 5-12 LKS32AT037PXL5M6Q9 Automatic addressing related parameter

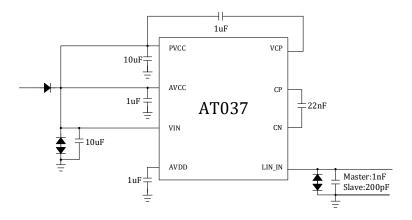

diagram 5-1 Power supply recommended application diagram

# 6 Analog Characteristics

| Parameter                            | Min. | Тур. | Max.     | Unit   | Description                                 |  |  |  |  |

|--------------------------------------|------|------|----------|--------|---------------------------------------------|--|--|--|--|

| ADC                                  |      |      |          |        |                                             |  |  |  |  |

| Supply voltage                       | 2.8  | 5    | 5.5      | V      | REF2VDD=0, ADC uses internal 2.4V reference |  |  |  |  |

| Supply voltage                       | 2.4  | 5    | 5.5      | V      | REF2VDD=1, ADC uses AVDD as reference       |  |  |  |  |

| Output bitrate                       |      | 1.2  |          | MHz    | f <sub>adc</sub> /20                        |  |  |  |  |

| Differential input signal            | -2.4 |      | +2.4     | V      | When Gain= 1; REF=2.4V                      |  |  |  |  |

| range                                | -3.6 |      | +3.6     | V      | When Gain=2/3;<br>REF=3.6V                  |  |  |  |  |

| Single-ended input sig-<br>nal range | -0.3 |      | AVDD+0.3 | V      | Limited by IO port input voltage            |  |  |  |  |

| DC offset                            |      | 5    | 10       | mV     | Correctable                                 |  |  |  |  |

| Effective number of bits (ENOB)      | 10.5 | 11   |          | bit    |                                             |  |  |  |  |

| INL                                  |      | 2    | 3        | LSB    |                                             |  |  |  |  |

| DNL                                  |      | 1    | 2        | LSB    |                                             |  |  |  |  |

| SNR                                  | 63   | 66   |          | dB     |                                             |  |  |  |  |

| Input resistance                     | 500k |      |          | Ohm    |                                             |  |  |  |  |

| Input capacitance                    |      | 10p  |          | F      |                                             |  |  |  |  |

| Reference voltage (REF)              |      |      |          |        |                                             |  |  |  |  |

| Supply voltage                       | 2.5  | 5    | 5.5      | V      |                                             |  |  |  |  |

| Output deviation                     | -9   |      | 9        | mV     |                                             |  |  |  |  |

| Power supply rejection ratio         |      | 70   |          | dB     |                                             |  |  |  |  |

| Temperature coefficient              |      | 20   |          | ppm/°C |                                             |  |  |  |  |

| Output voltage                       |      | 2.4  |          | V      |                                             |  |  |  |  |

|                                      | DAC  |      |          |        |                                             |  |  |  |  |

| Supply voltage                       | 2.5  | 5    | 5.5      | V      |                                             |  |  |  |  |

| Load resistance                      | 50k  |      |          | Ohm    |                                             |  |  |  |  |

| Load capacitance                     |      |      | 50p      | F      |                                             |  |  |  |  |

| Output voltage range                 | 0.05 |      | 3.0      | V      |                                             |  |  |  |  |

| Switching speed                      |      |      | 1M       | Hz     |                                             |  |  |  |  |

| DNL                                  |      | 1    | 2        | LSB    |                                             |  |  |  |  |

| INL                                  |      | 2    | 4        | LSB    |                                             |  |  |  |  |

| OFFSET                               |      | 5    | 10       | mV     |                                             |  |  |  |  |

| SNR                                  | 57   | 60   | 66       | dB     |                                             |  |  |  |  |

| Operational amplifier (OPA)          |      |      |          |        |                                             |  |  |  |  |

Table 6-1 LKS32AT037PXL5M6Q9 Analog Characteristics

| Parameter                               | Min. | Тур. | Max.  | Unit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-----------------------------------------|------|------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Supply voltage                          | 3.1  | 5    | 5.5   | V    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Bandwidth                               |      | 10M  | 20M   | Hz   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Load resistance                         | 20k  |      |       | Ohm  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Load capacitance                        |      |      | 5p    | F    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Common-mode input                       | 0    |      |       | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| range                                   | 0    |      | AVDD  | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Output signal range                     | 0    |      | 2*Vcm | V    | Minimum load resistance                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| OFFSET                                  |      | 10   | 15    | mV   | This OFFSET is the equivalent dif-<br>ferential input deviation obtained<br>when the OPA differential input is<br>short-circuited and OPA OUT is<br>measured from 0 level.<br>The output deviation of OPA is the<br>OPA magnification x OFFSET                                                                                                                                                                                                                 |  |  |

| Common Mode Voltage<br>(Vcm)            | 1.65 |      | 2.15  | V    | Measurement condition: normal<br>temperature.<br>Operational amplifier swing=2<br>× min(AVDD-Vcm, Vcm). It is<br>recommended that the applica-<br>tion using OPA single output<br>should be powered on to measure<br>Vcm and make software subtrac-<br>tion correction. For more analy-<br>sis, please refer to the official<br>website application note<br>"ANN009 - Differences between<br>Operational Amplifier Differential<br>and Single Operating Mode". |  |  |

| Common-mode rejec-<br>tion ratio (CMRR) |      | 80   |       | dB   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Power supply rejection<br>ratio (PSRR)  |      | 80   |       | dB   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Load current                            |      |      | 500   | uA   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Slew rate                               |      | 5    |       | V/us |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Phase margin                            |      | 60   |       | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Comparator (CMP)                        |      |      |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Supply voltage                          | 2.5  | 5    | 5.5   | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Input signal range                      | 0    |      | AVDD  | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| OFFSET                                  |      | 5    | 10    | mV   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Tuonomississi 1                         |      | 0.15 |       | uS   | Default power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Transmission delay                      |      | 0.6  |       | uS   | Low power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Hysteresis                              |      | 20   |       | mV   | HYS='0'                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Parameter | Min. | Тур. | Max. | Unit | Description |

|-----------|------|------|------|------|-------------|

|           |      | 0    |      | mV   | HYS='1'     |

| 5V LDO             |                       |      |      |                                      |                                      |  |  |  |

|--------------------|-----------------------|------|------|--------------------------------------|--------------------------------------|--|--|--|

| Input Voltage      | 7                     |      | 20   | V                                    |                                      |  |  |  |

| Output Voltage     | 4.75                  | 5    | 5.25 | V                                    | +/-5% Precision                      |  |  |  |

| Dropout Voltage    |                       | 2    |      | V                                    |                                      |  |  |  |

| Output Current     |                       | 40   |      | mA                                   |                                      |  |  |  |

| Ripple suppression |                       | 80   |      | dB                                   |                                      |  |  |  |

| Input Decoupling   | Input Decoupling 0.33 |      | uF   | Added to the VCCLDO pin, see pin de- |                                      |  |  |  |

| Capacitors         |                       | 0.55 |      | ur                                   | scription section                    |  |  |  |

| Output Decoupling  |                       | 1    |      | uЕ                                   | Added to the VCCLDO pin, see pin de- |  |  |  |

| Capacitor          |                       | 1    |      | uF                                   | scription section                    |  |  |  |

| Operating temper-  | -40                   |      | 125  | °C                                   |                                      |  |  |  |

| ature range        | -40                   |      | 125  | Ľ                                    |                                      |  |  |  |

Table 6-2 LKS32AT037PXL5M6Q9 5V LD0 Module parameters

Description of the analog register table:

The addresses 0x40000010-0x40000028 are the calibration registers for each module, which are provided with calibration values before being shipped from the factory. In general, you are not recommended to configure or change these values. To fine tune the analog parameters, you need to read the original calibration value.

The registers in the blank section must all be configured to 0 (reset to 0 when the chip is powered up). Other registers are configured as required by application scenarios.

### 7 Power Management System

#### 7.1 Power Supply System for the AVDD Pin

The power management system consists of an LDO15 module, a power detection module (PVD), and a power-on/power-off reset module (POR).

The AVDD internally supplies power to the LDO15 module, which supplies power to all internal digital circuits and PLL modules.

The LDO15 is automatically turned on after power-up and does not require software configuration, but the LDO15 output voltage can be fine-tuned by software.

The output voltage of LDO15 can be adjusted by setting the LDO15TRIM register, as described in the analog register table. LDO 15 has been calibrated before the chip leaves the factory.

The POR module monitors the voltage of the LDO15, and provides a reset signal for the digital circuit when the voltage of the LDO15 is lower than 1.1V (for example, at the beginning of power-up or at the time of power-down), so as to prevent the digital circuit from working abnormally.

### 8 Clock System

The clock system consists of an internal 64kHz RC clock, an internal 4MHz RC clock, and a PLL circuit.

The 64k RC clock is used as an MCU slow clock, like the reset filter module or an MCU clock in a low power state. The 4MHz RC clock is used as the MCU main clock and, when used in conjunction with the PLL, it can provide a clock up to 48MHz.

The 64k and 4M RC clocks are factory calibrated, the 4M RC clock has a customized calibration register to further calibrate the accuracy to  $\pm 0.5\%$ . In the temperature range of -40-105°C, the accuracy of the 64k RC clock is  $\pm 50\%$  and that of the 4M RC clock is  $\pm 1\%$  in this temperature range, 4M RC clock accuracy is  $\pm 2\%$  in  $-40\sim125$ °C.

The 4M RC clock is turned on by setting RCHPD = '0' (on by default, and off when set to '1'). The RC clock requires the Bandgap voltage reference module to provide reference voltage and current. Therefore, it is necessary to enable the BGP module before turning on the RC clock. The 4M RC clock is turned on and the BGP module is enabled by default in case of chip power-up. The 64k RC clock is always turned on and cannot be turned off.

The PLL multiplies the frequency of the 4M RC clock, to ensure a higher-speed clock for modules such as MCU, ADC, etc. The highest clock of the MCU and PWM modules is 48MHz, while the typical clock of the ADC module is 24MHz.

The PLL module is enabled by setting PLLPDN = '1' (off by default, and on when set to 1). The BGP (Bandgap) module needs to be enabled before the PLL module. After enabling the PLL module, it will take a stabilization time of 6us to output a stable timer. By default when the chip is powered on, the RCH timer is turned on and the BGP module is enabled; however, the PLL module is disabled, and needs to be enabled with software.

# 9 Reference Voltage Source

The reference voltage source provides reference voltage and current for the ADC, DAC, RC timer, PLL, temperature sensor, operational amplifier, comparator, and FLASH. The reference voltage source of BGP needs to be enabled before using any of these modules.

The BGP module is enabled by default when the chip is powered on. The reference voltage source is enabled by setting BGPPD = '0', and BGP needs about 2us to stabilize from being enabled to disabled. The output voltage of BGP is about 1.2V with an accuracy of  $\pm 0.8\%$

### **10 ADC Module**

A SAR ADC is integrated into the chip. The ADC module is disabled by default when the chip is powered on. Before the ADC is enabled, it is necessary to enable the BGP and PLL modules, turn on the 4M RC timer, and select the ADC operating frequency. The ADC operating timer is 24 M by default.

The ADC requires at least 17 ADC timer cycles to complete a conversion, of which 12 are conversion cycles and 5 are sampling ones. The sampling period can be set by configuring the SAMP\_TIME register in SYS\_AFE\_REG2. It is required to set not less than 3 sampling periods, that is, more than 8 ADC clocks.

The recommended value is 3, which corresponds to an output data rate of 1.2MHz for the ADC.

The ADC operates in the following modes: single single-channel trigger, continuous single-channel trigger, single 1-16 channel scanning, and continuous 1-16 channel scanning. Each ADC has 16 independent sets of registers for each channel.

The ADC trigger event may come from external timer signals T0, T1, T2, T3 for a preset number of times, or may be triggered by software.

The ADC has two gain modes that are set by SYS\_AFE\_REG0.GA\_AD, corresponding to 1 x time and 2/3 x times gains. The 1 x time gain corresponds to an input signal of  $\pm 2.4$ V, and the 2/3 x times gain corresponds to an input signal amplitude of  $\pm 3.6$ V. In measuring the output signal of an operational amplifier, the specific ADC gain is selected based on the maximum possible output signal of the operational amplifier.

### **11 Operational Amplifier**

Two input and output rail-to-rail operational amplifiers, with a built-in feedback resistor R2/R1. External pins should be connected in series with a resistor R0. The value of resistance of the feedback resistors R2:R1 can be set via register RES\_OPA <1:0> for different magnification. The values corresponding to the specific registers are described in the analog register table.

The final magnification is R2/(R1+R0), where R0 is the value of resistance of the external resistor.

A capacitor greater than or equal to 15pF is required to be connected across the two input pins of the op amp.

For applications of direct sampling of MOS transistor resistor, it is recommended to connect an external resistor of >20k $\Omega$  to reduce the current flowing into the chip pins when the MOS transistor is turned off.

For small resistor sampling applications, external resistors of  $100\Omega$  are recommended.

The amplifier can select the output signal in the amplifier by setting OPAOUT\_EN to send it to P0.7 IO port through BUFFER for measurement and application. Because BUFFER exists, it is also possible to send one output signal of the op amp under its normal operation mode.

In the default state when the chip is powered up, the amplifier module is turned off. The amplifier can be enabled by setting OPAPDN = '1' and the BGP module should be enabled before enabling the amplifier.